# Avaliação dos Padrões de Escrita de Benchmarks de STM

#### Michael Alexandre Costa

Felipe Leivas Teixeira Maurício Lima Pilla André Rauber Du Bois

Universidade Federal de Pelotas {macosta, flteixeira, pilla, dubois}@inf.ufpel.edu.br

Abril de 2015

1 Introdução

Introdução

- 2 Phase Change Memory PCM

- **3** Software Transactional Memory STM

- 4 Metodologia

- Resultados

- 6 Conclusão

- 1 Introdução

- 2 Phase Change Memory PCM

- **3** Software Transactional Memory STM

- 4 Metodologia

- 5 Resultados

- 6 Conclusão

# Introdução

#### **Memórias Transacionais**

Memórias Transacionais ou *Software Transactional Memory* (STM) é uma alternativa de sincronização

## Phase Change Memory (PCM)

Phase Change Memory (PCM) é uma nova alternativa às memórias DRAMs

## Objetivo

O objetivo do trabalho é estender a análise do comportamento das escritas *benchmarks* de STMs com impacto em memórias PCM

- 1 Introdução

- 2 Phase Change Memory PCM

- **3** Software Transactional Memory STM

- 4 Metodologia

- 5 Resultados

- 6 Conclusão

# **Phase Change Memory - PCM**

### **Caracter**ística

Utiliza mudança de fase do seu material para armazenar os dados

### **Vantagens**

- Consumo de Energia

- Tempo de Leitura

### **Desvantagens**

- Desgaste do Material

- Tempo de Escrita

# **Phase Change Memory - PCM**

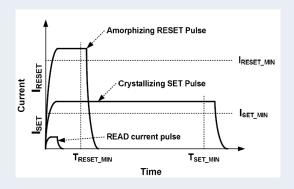

## Comportamento das leiuras e escritas PCM [Wang and Wu 2009]

- 1 Introdução

- 2 Phase Change Memory PCN

- **3** Software Transactional Memory STM

- 4 Metodologia

- 5 Resultados

- 6 Conclusão

# **Software Transactional Memory - STM**

### Características

- Desenvolvida para reduzir as dificuldades e limitações

- Permite:

- Programação de alto nível

- Reuso de código

- Sem Deadlock

### Transações

- Atomicidade

- Isolamento

## Exemplo de código de Memórias Transacionais

```

public void deposita( double quantia ) {

atomic {

if( quantia > 0 ) {

this.saldo += quantia;

}

}

}

```

- 1 Introdução

- 2 Phase Change Memory PCN

- **3** Software Transactional Memory STM

- 4 Metodologia

- 5 Resultados

- 6 Conclusão

Introdução PCM STM Metodologia Resultados Conclusão

# Metodologia

#### **Bibliotecas**

Biblioteca de Memórias Transacionais: TinySTM

#### **Ferramentas**

Ferramenta de Instrumentação: PinTools

#### **Benchmark**

O Benchmark utilizado foi o STAMP

### Instrumentação

Para desenvolver o trabalho foi implementado uma instrumentação que faz a contagem do número de escrita feita à memória

# Metodologia

### Metodologia

Foram medidas dez execuções para cada cenário

- 1, 2, 4, 8, 16, 32 e 64 threads

- Com instrumentação

## Máquina

Composta por quatro nós de processamento AMD Opteron 6276 com 2,3GHz e três níveis de cache (L3 de 6MB, L2 de 2MB e L1 de 64KB). Cada nó de processamento contém 16 cores, somando um total de 64. Esta máquina possui 128GB de memória principal, sendo 32GB por nó separados em blocos de 16GB.

- 1 Introdução

- 2 Phase Change Memory PCN

- **3** Software Transactional Memory STM

- 4 Metodologia

- **5** Resultados

- 6 Conclusão

# Resultados

### Análise do Resultados

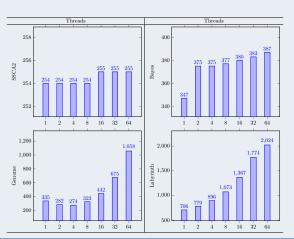

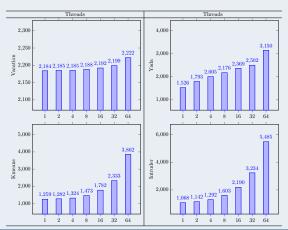

Os *benchmarks* mostram diferentes valores nos números de escritas para cada cenário de *thread* apresentado

Introdução PCM STM Metodologia **Resultados** Conclusão

# Resultados

Comportamento das escritas em relação ao aumento do número de threads

Introdução PCM STM Metodologia **Resultados** Conclusão

## Resultados

Comportamento das escritas em relação ao aumento do número de threads (cont.)

- 1 Introdução

- 2 Phase Change Memory PCN

- **3** Software Transactional Memory STM

- 4 Metodologia

- 5 Resultados

- 6 Conclusão

#### Trabalho Realizado

Foi feita uma analise estendida do comportamento das escritas apresentado em [Teixeira et al. 2014]

### Considerações Finais

Os resultados mostraram padrões nas escritas STMs:

- Na maioria dos benchmarks com um aumento do número de threads temos um aumento no número de escritas

- Nos cenários de 32-64 threads notamos um aumento maior no número de escritas em relação as outras threads

### **Trabalhos Futuros**

- Analisar os padrões de escritas utilizando outras bibliotecas STMs

- Estender outras abordagens feitas no artigo [Teixeira et al. 2014]

Teixeira, F., Pilla, M., Du Bois, A., and Mossé, D. (2014). Profiling patterns of bit flipping for software transactional memories. In 26th International Symposium on Computer Architecture and High Performance Computing - SBAC-PAD.

Wang, F. and Wu, X. (2009).

Non-volatile memory devices based on chalcogenide materials. *Information Technology: New Generations, Third International Conference on*, 0:5–9.

# Avaliação dos Padrões de Escrita de Benchmarks de STM

#### Michael Alexandre Costa

Felipe Leivas Teixeira Maurício Lima Pilla André Rauber Du Bois

Universidade Federal de Pelotas {macosta, flteixeira, pilla, dubois}@inf.ufpel.edu.br

Abril de 2015