# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Brazilian Computer Society - SBC Brazilian Microelectronics Society - SBMicro Center for Advanced Microelectronics Technology - CEITEC IEEE Circuits and Systems Society - Region 9 - Chapter RS IEEE Student Branch UFRGS

IEEE-CAS Student Branch UFRGS

# **SIM 2008**

# 23<sup>rd</sup> South Symposium on Microelectronics

# **Proceedings**

**General Chair**

Marcelo Johann

**Editors**

Alessandro Girardi Juan Pablo Martinez Brito

Published by

**SBC**

Bento Gonçalves, May 5-6, 2008

UFRGS - II - GME Av. Bento Gonçalves, 9500 - Bloco IV Caixa Postal 15064 CEP 91501-970 - Porto Alegre - RS - BRASIL Phone: +55 51 3308 6155 Fax: +55 51 33087308 www.sbc.org.br/sim

#### CIP - CATALOGAÇÃO NA PUBLICAÇÃO

South Symposium on Microelectronics (23. : 2008 : Porto Alegre, RS, Brazil).

Proceedings / XXIII South Symposium on Microelectronics,; editors Alessandro Girardi, Juan Pablo Marinez Brito. – Porto Alegre : SBC, 2008. 192 p. : il.

ISBN 978-85-7669-117-4

Conhecido também como SIM 2008.

1. Microeletrônica. I. Girardi, Alessandro. II. Brito, J. P. M. IV. SIM (23. : 2008 : Porto Alegre). V. Proceedings.

Printed in Porto Alegre, Brazil.

Cover: Ricardo Augusto da Luz Reis (UFRGS) Logo by Ricardo Augusto da Luz Reis (UFRGS)

#### **Foreword**

Welcome to the 23rd edition of the South Symposium on Microelectronics. This symposium, originally called Microelectronics Internal Seminar (SIM), started in 1984 as an internal workshop of the Microelectronics Group (GME) at the Federal University of Rio Grande do Sul (UFRGS) in Porto Alegre. From the beginning, the main purpose of this seminar was to offer the students an opportunity for practicing scientific papers writing, presentation and discussion, as well as to keep a record of research works under development locally.

The event was renamed as South Symposium on Microelectronics in 2002 and transformed into a regional event, reflecting the growth and spreading of teaching and research activities on microelectronics in the region. The proceedings, which started at the fourth edition, have also improved over the years, receiving ISBN numbers, adopting English as the mandatory language, and incorporating a reviewing process that also involves students. Works submitted to this seminar may represent different levels of research activity, ranging from early undergraduate research assistant assignments to advanced PhD works in cooperation with companies and research labs abroad. The review process is therefore an important step to train young students and to provide feedback that helps to improve fresh new papers that may further be submitted to nationwide and international conferences.

This year SIM takes place at Bento Gonçalves togheter with the 10<sup>th</sup> edition of the regional microelectronics school (EMICRO), a series of basic and advanced short courses provided by local professors and invited speakers.

These proceedings include 36 papers organized in 8 topics: CAD tools, analog and RF design, networks-on-chip, image and video processing, digital design and fault tolerance.

We would finally like to thank all individuals and organizations that helped to make this event possible. SIM 2008 was co-organized together with EMICRO UFRGS, promoted by the Brazilian Computer Society (SBC), the Brazilian Microelectronics Society (SBMicro) and IEEE CAS Region 9, receiving financial support from FINEP and Fapergs Brazilian agencies. Special thanks go to the authors and reviewers that spent precious time on the preparation of their works and helped to improve the quality of the event.

Bento Gonçalves, May 5, 2008 Alessandro Girardi Juan Pablo Martinez Brito Marcelo Johann

#### **XXIII SIM - South Symposium on Microelectronics**

Bento Gonçalves – RS – Brazil May 5-6, 2008

#### General Chair

Marcelo de Oliveira Johann (UFRGS) – *johann@inf.ufrgs.br*

#### **SIM Program Chairs**

Alessandro Girardi (UNIPAMPA) – *alessandro.girardi@unipampa.edu.br* Juan Pablo Martinez Brito (UFRGS) – *juan@inf.ufrgs.br*

#### **EMICRO Program Chairs**

Ricardo Augusto da Luz Reis (UFRGS) – reis@inf.ufrgs.br Julio Leão da Silva Jr. (CEITEC) – julio@ceitec.org.br

#### List of Reviewers

Adriel Ziesemer Junior

André Mariano

André Aita

Braulio Mello

Bruno Zatt

Caio Alegretti

Carolina Neves

Cláudio Diniz

Cristiano Lopes

Cristina Meinhardt

Dalton Colombo

Eduardo Conrad Junior

Eduardo Flores

Eduardo Costa

Fábio Ramos

Felipe Marques Fernando Paixão Cortes

Filipe Vieira

François Rivet

Guilherme de Freitas

Guilherme Corrêa

Júlio C. B. Mattos

José Augusto Nacif

Josue de Freitas

Juan Pablo Martinez Brito

Leandro Rosa

Leandro Pieper

Leomar Rosa Jr

Lisane Brisolara

Luciano Agostini

Luciano de Paula

Luiz Fernando Ferreira

Marcelo Porto

Matheus Braga

Márcio Kreutz

Murilo Pesati

Paulo Butzen

Rafael Cancian

Rafael Soares

Reginaldo Tavaves

Sandro Silva

Sandro Soares

Sidinei Ghissoni

Thaísa Silva

Thiago Assis

# **Table of Contents**

| ANALOG & RF DESIGN                                                                                                                       |        |

|------------------------------------------------------------------------------------------------------------------------------------------|--------|

| A Study on Components Sizing for CMOS Bandgap Voltage References Rafael Tambara Blumer, Filipe Costa Beber Vieira, Cesar Ramos Rodrigues |        |

| Device Characterization of an IBM 0.18                                                                                                   | 13     |

| Giovano da Rosa Camaratta, Eduardo Conrad Jr, Luiz Fernando Ferreira,                                                                    |        |

| Fernando Paixão Cortes, Sergio Bampi                                                                                                     |        |

| Accurate Method for Subthreshold and Gate Leakage Current Estimati                                                                       | on     |

| in CMOS Complex Gates                                                                                                                    |        |

| P. F. Butzen, L. S. da Rosa Jr, E. J. D. Chiappetta Filho, D. S. Moura,<br>A. I. Reis, R. P. Ribas                                       | 25     |

| A 65nm CMOS Analog Processor for Mobile Terminals Software Radio                                                                         |        |

| Front End                                                                                                                                |        |

| François Rivet, Yann Deval, Domnique Dallet, Jean-Baptiste Begueret,                                                                     |        |

| Didier Belot, Philippe Cathelin                                                                                                          | 29     |

|                                                                                                                                          |        |

|                                                                                                                                          |        |

| NETWORKS-ON-CHIP                                                                                                                         |        |

|                                                                                                                                          |        |

| Functional Test of Networks-on-Chip: Test of Routers  Pedro Almeida, Marcelo Lubaszewski, Marcos Hervé,                                  |        |

| Fearo Almeiaa, Marceio Lubaszewski, Marcos Herve, Fernanda Lima Kastensmidt, Érika Cota                                                  | 35     |

| <b>Soft Cores for Performance Evaluation of NoCs in FPGA</b>                                                                             |        |

| Thiago Felski Pereira, Cesar Albenes Zeferino                                                                                            | 41     |

| A SystemC-based Environment                                                                                                              |        |

| for Performance Evaluation of Networks-on-Chip                                                                                           |        |

| Jaison Valmor Bruch, Rafael Luiz Cancian, Cesar Albenes Zeferino                                                                         | 45     |

| <b>Automatic Code Generation for Embedded</b>                                                                                            |        |

| Applications from Verified Alloy Models                                                                                                  |        |

| Ronaldo Ferreira, Emilena Specht, Lisane Brisolara, Érika Cota, Luigi Carro                                                              | 49     |

|                                                                                                                                          |        |

|                                                                                                                                          |        |

| CAD TOOLS I                                                                                                                              |        |

| Denformer of Driver Denting and Interconnect Delay Medals                                                                                |        |

| Performance-Driven Routing and Interconnect Delay Models T. J. Reimann, G. B. V. Santos, M. O. Johann, R. A. L. Reis                     | 5.5    |

| Improving Pathfinder using Iterated 1-Steiner Algorithm                                                                                  | 55     |

| Luca Bochi Saldanha, Charles Capella Leonhardt, Adriel Mota Ziesemer Junior, Ricardo Augusto a                                           | la     |

| Luz Reis                                                                                                                                 |        |

| Timing-Aware Placement Algorithm to 3D Circuits                                                                                          |        |

| Felipe Pinto Guilherme Flach, Renato Hentschke, Ricardo Reis                                                                             | 63     |

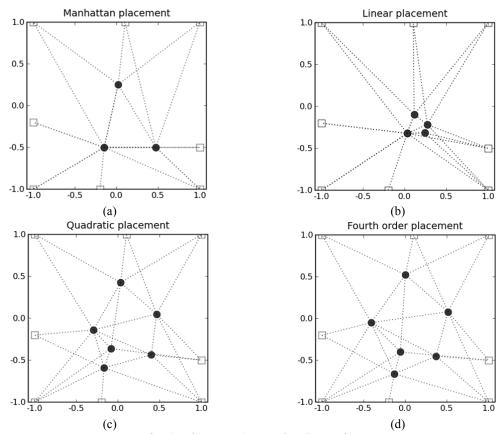

| Manhattan Placement by Linear Programming                                                                                                | 47     |

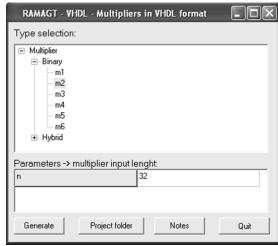

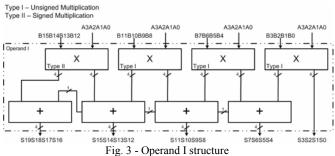

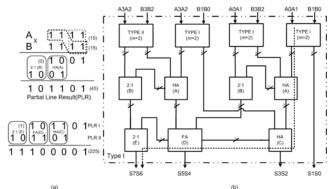

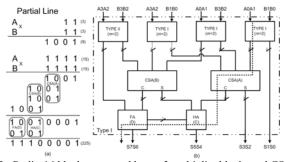

| RAMAGT - Radix-2 <sup>m</sup> Array Multipliers Automatic Generation Tool                                                                | 0/     |

| Diego P. Jaccottet, Jonatas M. Roschild, Leandro Z. Pieper, Eduardo A. Costa, Sérgio J. de Almeio                                        | la 71  |

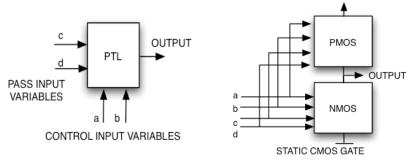

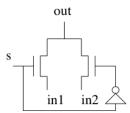

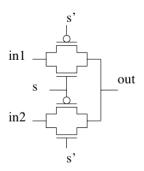

| Dynamic Power Dissipation in Pass Transistor Circuits                                                                                    | .u / 1 |

| Paginaldo da N. Tayanas                                                                                                                  | 75     |

# FAULT TOLERANCE

| Asymmetric and Symmetric Transistor Sizing to Reduce SET Sensitivity                                                     | in       |

|--------------------------------------------------------------------------------------------------------------------------|----------|

| Integrated Circuits                                                                                                      |          |

|                                                                                                                          |          |

| Modeling of a NMOS 90 nm device to Multiple Event Transient Simulati                                                     | ion      |

| A Two-Step SET Sensitivity Estimation Technique  Matheus P. Braga, Guilherme Corrêa, Luciano Agostini, José Luís Güntzel | 89       |

| Fault-Tolerant Fast Adders Implemented in FPGAs                                                                          |          |

|                                                                                                                          | 93       |

| DIGITAL DESIGN                                                                                                           |          |

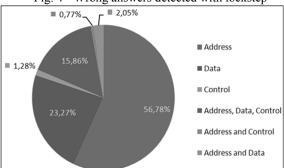

| An experimental analysis of the lockstep architecture                                                                    |          |

|                                                                                                                          | 99       |

|                                                                                                                          |          |

|                                                                                                                          | 105      |

|                                                                                                                          | 103      |

|                                                                                                                          | 109      |

|                                                                                                                          |          |

| Leandro Zafalon Pieper, Eduardo A. C. Costa, Sergio J. M. de Almeida, Sérgio Bampi, José C. Mont                         |          |

|                                                                                                                          |          |

|                                                                                                                          |          |

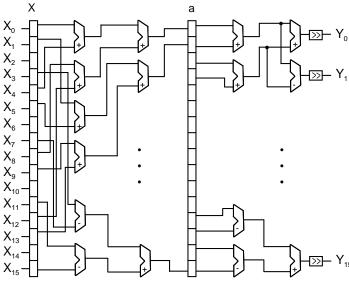

| 4:2 Adder Compressor for the T Block's Forward 4x4 Hadamard                                                              |          |

| Transform of the H.264/AVC Video Compression Standard                                                                    |          |

|                                                                                                                          | 121      |

| Cristiano Lazzari, Thiago Assis, Fernanda Lima Kastensmidt, Gilson Wirth, Lorena Anghel, Ricardo Rets                    |          |

|                                                                                                                          |          |

|                                                                                                                          | 125      |

|                                                                                                                          |          |

|                                                                                                                          | <b>J</b> |

|                                                                                                                          | 131      |

|                                                                                                                          |          |

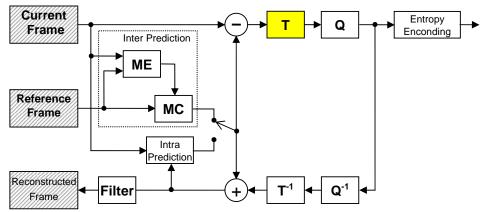

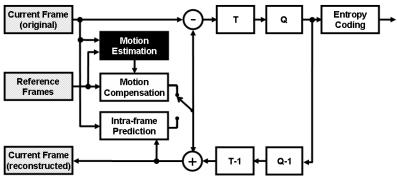

| H.264/AVC Standard Focusing in the Intra Frame Coder                                                                     |          |

| Fabiane Rediess, Felipe Sampaio, Carolina Fonseca,                                                                       | 105      |

| Sergio Bampi, Altamiro Susin, Luciano Agostini                                                                           | .135     |

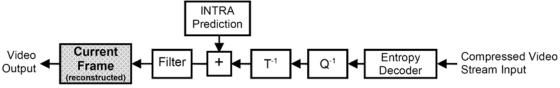

# **IMAGE & VIDEO PROCESSING II**

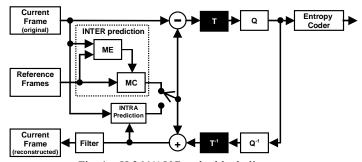

| Reference C Software H.264/AVC Decoder for Hardware Debug and Validation                                                                                                                                                            |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Márlon A. Lorencetti, Wagston T. Staehler, Altamiro A. Susin                                                                                                                                                                        | 141          |

| Architecture Design and Prototyping of a Fully Parallel H.264/AVC Hadamard Transform Targeting Real Time in Very High Resolution Videos  Felipe Sampaio, Carolina Fonseca, Fabiane Rediess, Sergio Bampi, Altamiro Susin, Luciano A | 2x2  gostini |

| A High Throughput Diamond Search Architecture for HDTV Motion Estimation                                                                                                                                                            | 1            |

| Marcelo Porto, Luciano Agostini, Sergio Bampi, Altamiro Susin                                                                                                                                                                       |              |

| Level Decoder Architecture for CAVLD of H.264 Video Compression Standard                                                                                                                                                            | 1            |

| João Vortmann, Thaísa Silva, Luciano Agostini, Altamiro Susin, Sergio Bampi                                                                                                                                                         |              |

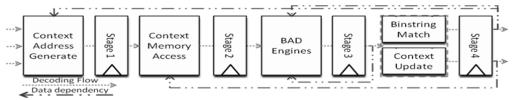

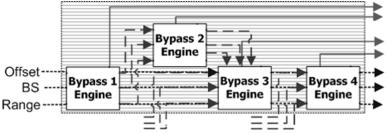

| High Efficiency Hardware Design for Binary Arithmetic Decoder Engo of CABAD Based on Bitstream Flow Analysis                                                                                                                        | C            |

| Dieison Antonello Deprá, Claudio Diniz, Bruno Zatt, Sergio Bampi                                                                                                                                                                    | 157          |

| CAD TOOLS II                                                                                                                                                                                                                        |              |

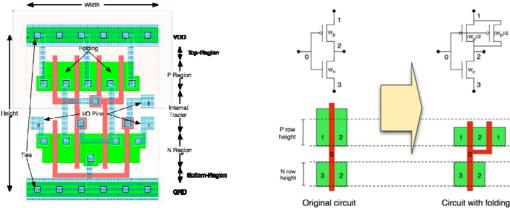

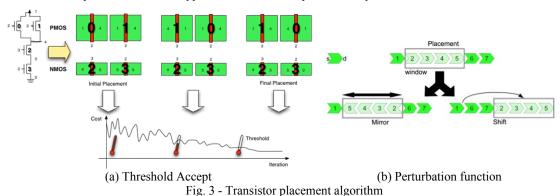

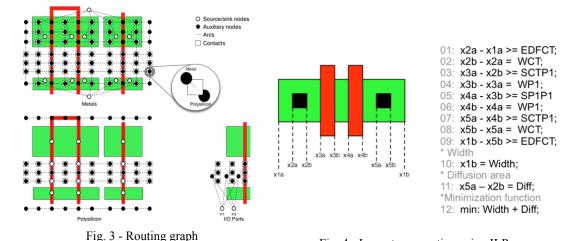

| Cellgen - An Automatic Cell Synthesis Tool  Adriel Ziesemer Jr., Ricardo Reis                                                                                                                                                       | 175          |

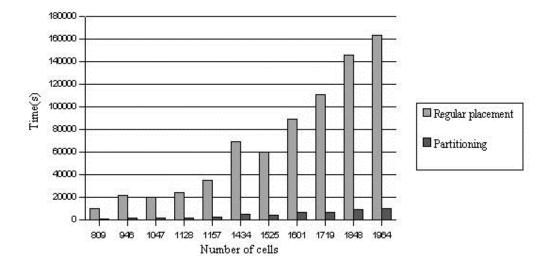

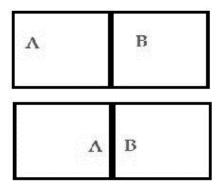

| Partitioning in the PARROT Flow for Physical Synthesis Samuel Nascimento Pagliarini, Glauco Borges Valim dos Santos, Ricardo Reis                                                                                                   |              |

| Design Methodology for Cell Library Testbench Circuit  S. Bavaresco, M. Lubaszewski, A. I. Reis, R. P. Ribas                                                                                                                        |              |

| Standard Cell Design Flow for H.264 Luma Motion Compensation Architecture                                                                                                                                                           |              |

| Thaísa Silva, Érico Sawabe, Luciano Agostini, Altamiro Susin, Sergio Bampi                                                                                                                                                          | 179          |

| William Lautenschläger, Ricardo Reis                                                                                                                                                                                                | 185          |

|                                                                                                                                                                                                                                     | 100          |

| XXIII SIM - South Symposium on Microelectronics | 11 |

|-------------------------------------------------|----|

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

| ANALOG & RF DESIGN                              |    |

|                                                 |    |

|                                                 |    |

|                                                 |    |

# A Study on Components Sizing for CMOS Bandgap Voltage References

<sup>1</sup>Rafael Tambara Blumer, <sup>1</sup>Filipe Costa Beber Vieira, <sup>1,2</sup>Cesar Ramos Rodrigues raftamb@mail.ufsm.br, filipecbv@mail.ufsm.br, cesar@ieee.org

<sup>1</sup>GMICRO - Microeletronics Group <sup>2</sup> Electrical Engineering Department Federal University of Santa Maria, UFSM Santa Maria, Brazil

#### **Abstract**

The bandgap reference (BGR) is a block extensively used in analog circuits in implementation voltage references. This topology is widely used due its good performance and simplicity of operation. However, factors deriving from process variations limits the performance of the BGR. To circumvent this problem, a method for matching its components is proposed. This methodology trades with process parameters and power consumption to achieve a compromise between area and matching. The circuit was designed in XFAB-0.6  $\mu$ m CMOS technology, has an output voltage of 1.268 V and consumes 40  $\mu$ A. The area occupied by the BGR is  $400x230~\mu$ m<sup>2</sup>. The circuit is currently being fabricated.

#### 1. Introduction

The bandgap reference (BGR) is one of most used architectures for voltage reference implementation. Main characteristic of references is stability. It is desirable that they can generate a fixed voltage, with immunity to power supply, temperature and variations in parameters during the fabrication process. For these reasons, the BGR are commonly found in ADCs, DACs, DRAMs, flash memories and variable gain amplifiers.

Many studies are being developed for designing high performance CMOS BGRs circuits. Although, components tolerance, and process variations severely degrades BGR performance [BRI 07]. To contribute on this issue, a simple design procedure is presented in this paper. In the proposed methodology transistors and resistors are sized aiming the best component matching for a given power consumption.

In the section 2, we describe the operational characteristics of a BGR circuit. The design procedure and theory about the matching components is developed in section 3. The section 4 shows the simulated results. The circuit layout and final conclusions are presented in the section 5 and 6 respectively.

# 2. Circuit Description

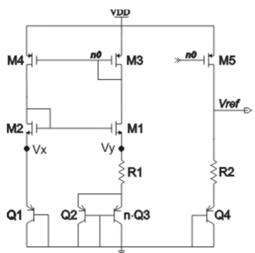

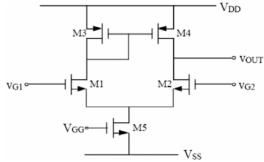

The schematic of BGR circuit studied in this paper is shown in fig. 1.

Fig. 1 – Basic structure of the BGR circuit.

This topology follows the basic principles of operation from BGRs: supply-independent biasing and temperature-independent reference signal generation [RAZ 01].

Supply-independent biasing aims stability of the signal reference with respect to  $V_{DD}$  oscillations. This feature requires that the circuit must bias itself. Auto biasing is obtained with the feedback action in current mirrors  $M_1$ - $M_3$  and  $M_2$ - $M_4$ .

The generation of temperature-independent reference is another condition for BGR operation. Assuming that  $M_1$ - $M_2$  e  $M_3$ - $M_4$  are identical pairs, we note that  $V_X = V_Y$  when  $I_{DI} = I_{D2}$ . Considering these conditions, and all transistors operating in strong inversion, the voltage on the  $R_I$  can be expressed as (1).

$$V_{R1} = V_T \cdot \ln(n) \tag{1}$$

Consequently, the current of M<sub>1</sub> and M<sub>2</sub> transistors are given by:

$$I_{D1} = I_{D2} = \frac{V_T \cdot \ln(n)}{R_1} \,. \tag{2}$$

From the current mirror  $M_3$ - $M_5$ , an output voltage  $V_{ref}$  is obtained as follows:

$$V_{ref} = I_{D5} \cdot R_2 + V_{BE4} = \left[ \frac{(W/L)_5}{(W/L)_3} \cdot \frac{V_T \cdot \ln(n)}{R_1} \right] \cdot R_2 + V_{BE4}. \tag{3}$$

Deriving (3) as a function of temperature and considering  $R_1 = R_2$ , we obtain:

$$\frac{\partial V_{ref}}{\partial T} = \frac{(W/L)_5}{(W/L)_3} \cdot \frac{K}{q} \cdot \ln(n) + \frac{\partial V_{BE4}}{\partial T} = 0 \Rightarrow K_{ref} = \frac{(W/L)_5}{(W/L)_3} = \frac{\frac{-\partial V_{BE4}}{\partial T}}{\frac{K}{q} \cdot \ln(n)},$$

(4)

where K is the Boltzmann's constant, q is the electronic charge,  $\partial V_{BE4} / \partial T = -1.826 mV / ^{\circ}C$  and n ratio between currents from Q<sub>3</sub> and Q<sub>2</sub> transistors. Equation (4) establishes the current mirror (M<sub>3</sub>-M<sub>5</sub>) gain.

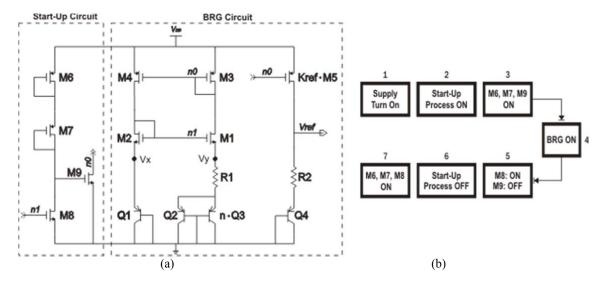

In fig. 3 (a), the full BGR schematic is shown, including the start-up circuit. This circuit drives the BGR out of the degenerates bias point when the supply is turn on. The blocks diagram of fig. 3 (b) show operation stages of the start-up circuit.

Fig. 3 – BGR circuit: a) Complete schematic; b) Operation stages of the start-up circuit.

The M<sub>6</sub>-M<sub>7</sub> transistors must have long channels to avoid an excessive current consumption after the start-up process.

#### 3. Circuit Design

This section presents a different way for sizing the BGR components in fig. 1. The mathematical routine uses the current consumption specification as starting point.

#### I. Resistor design

One of the most important characteristic of an electric circuit is the current consumption  $I_S$ . After the startup circuit is disabled, the total consumption must be equal to the summation of currents from  $M_1$ ,  $M_2$ , and  $M_5$ :

$$I_S = I_{D1} + I_{D2} + I_{D5}. (5)$$

From fig.3, we can see that currents  $I_{DI}$ ,  $I_{D2}$  and  $I_{D5}$  are related by aspect ratios from the transistors of the current mirrors, thus

$$I_{D2} = I_{D1}$$

, and (6)

$$I_{D5} = K_{REF} \cdot I_{D1}. \tag{7}$$

Substituting (1), (6) and (7) in equation (5) and considering  $R_1 = R_2$ , we can determine the circuit resistance values as a function of  $I_S$ :

$$R_1 = R_2 = \frac{V_T \cdot \ln(n) \cdot (2 + K_{ref})}{I_S}$$

(8)

The standard deviation between resistances of two identical rectangular devices depends on their areas [PEL 89]. This relation can be expressed as:

$$\sigma R \left( \frac{\Delta R}{R} \right) = \frac{A_R}{\sqrt{AREA_{resistor}}} \ . \tag{9}$$

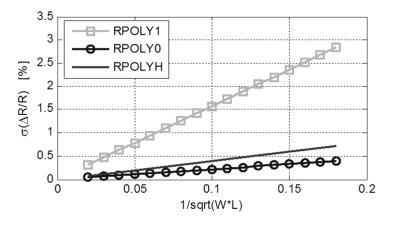

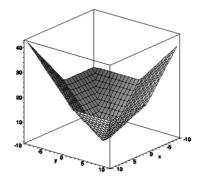

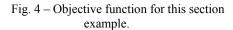

Equation (9) is provided by foundry to model mismatching between resistors. The constant  $A_R$  is a process parameter and depends on the resistor type chosen in the project. For XFAB-0.6  $\mu$ m CMOS technology, this data can be extracted from graph in fig. 4.

Fig. 4 – Poly resistor matching XC06.

Thus, using information from fig. 4, one can choose resistor type and correspondent sheet resistance ( $R_{\square}$ ). The required resistance for BGR circuit can be defined from equations (10) trough (12):

$$R = R_{\Box} \cdot N_{\Box} \tag{10}$$

$$W_{resistor} = \sqrt{\frac{AREA_{resistor}}{N_{\Box}}} \qquad (11) \qquad L_{resistor} = W_{resistor} \cdot N_{\Box} \qquad (12)$$

where  $N_{\square}$  define a square numbers used for reach the desire resistance.

#### Π. Transistors design

The threshold voltage and the current factor are the main sources of mismatching between MOS transistors. These random variations have a normal distribution with zero mean and standard deviation that depends on the area and the spacing between the components [PEL 89]. The current difference between two identical transistors is quantified according to data provided by foundry as follows:

$$\sigma\left(\frac{\Delta ID}{ID}\right) = \frac{AIDx}{\sqrt{W \cdot L}} \xrightarrow{\text{with}} x = (V_{gs} - V_{th})$$

(13)

where AIDx is a process parameter that is strongly dependent from the overdrive gate voltage  $(V_{gs}-V_{th})$  [XFA 05]. The foundry provides some AIDx values for specific bias conditions. The tab.1 shows the relation between the process parameter AIDx and  $(V_{gs}-V_{th})$ .

Tab.1 - Typical AIDx values for NMOS4 e PMOS4 devices.

| Device | AID0.0 | AID0.2 | AID0.4 | AID0.6 | AID1.0 | AID2.0 | AID3.0 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| NMOS4  | 15.9   | 9.11   | 6.3    | 4.91   | 3.02   | 1.74   | 1.39   |

| PMOS4  | 24.8   | 10.8   | 6.34   | 4.44   | 2.86   | 1.74   | 1.41   |

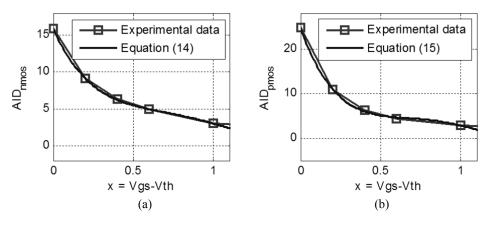

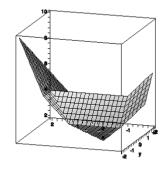

As Tab.1 presents only few operational conditions, equations were created to provide the intermediate solutions. These equations were created by curve fitting and can be expressed by equations (14)-(15). The results are compared to XFAB measures in fig. 5.

$$AID_{NMOS}(x) = -4.6 \cdot x^5 + 32.2 \cdot x^4 - 78.7 \cdot x^3 + 86.3 \cdot x^2 - 48 \cdot x + 15.8 \tag{14}$$

$$AID_{PMOS}(x) = -10.5 \cdot x^5 + 73.7 \cdot x^4 - 182.1 \cdot x^3 + 198.6 \cdot x^2 - 101.6 \cdot x + 24.7 \tag{15}$$

Fig. 5 – Process Parameter AIDx: a) AID<sub>nmos</sub>; b) AID<sub>pmos</sub>

The correct use of equation (13) requires a calibration of AIDx as a function of  $(V_{gs}-V_{th})$ . The  $V_{gs}$  value is approximated from simulated  $I_{DS}$  x  $V_{gs}$  curves, for NMOS and PMOS transistors with large dimensions (100µmx100µm), according to the current obtained from equation (2). Then, drawing square transistors and the current mismatching devices as  $\sigma(\Delta ID/ID)$ , W-L dimensions for NMOS (M<sub>1</sub>,M<sub>2</sub>) and PMOS (M<sub>3</sub>,M<sub>4</sub>) could be calculated for the specified mismatch as:

$$W_{NMOS} = L_{NMOS} = \frac{AIDx_{NMOS}}{\sigma(\Delta ID / ID)}$$

(16)

$$W_{PMOS} = L_{PMOS} = \frac{AIDx_{PMOS}}{\sigma(\Delta ID / ID)}.$$

(17)

Following the above routine, a BGR circuit with  $\sigma(\Delta R/R) = \sigma(\Delta ID/ID) = 0.1\%$ , current consumption of  $40\mu A$  was projected for standard *RPOLY0* layer. Final dimensions obtained are shown in tab.2.

| Tab.2 – Design Values |                                                          |  |  |  |

|-----------------------|----------------------------------------------------------|--|--|--|

| Component             | Value                                                    |  |  |  |

| M1, M2                | $W = L = 79 \mu m$                                       |  |  |  |

| M3, M4, M5            | $W = L = 61 \mu m$                                       |  |  |  |

| M6, M7                | $W = 1 \mu m$ , $L = 20 \mu m$                           |  |  |  |

| M8, M9                | $W = 10 \mu m$ , $L = 1 \mu m$                           |  |  |  |

| Q1Q4                  | 25 μm² (QPV5 Vertical BJT)                               |  |  |  |

| R1, R2                | $W = 4 \mu m$ , $L = 112 \mu m - 16.75 k\Omega (RPOLY0)$ |  |  |  |

# 4. Simulations Results

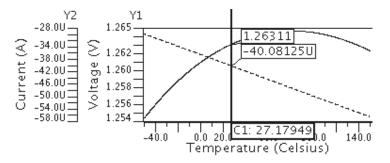

The BGR circuit from Fig. 3 (a) was simulated. The graph in fig. 6 depicts output voltage  $V_{ref}$  and the current  $I_S$  as a function of temperature. The circuit is supplied with 5 V.

Fig. 6 – Reference voltage and consumed current as a function of temperature.

As expected, the output voltage and consumed current at 27 °C are 1.263 V and 40.08  $\mu$ A respectively. The total variation on the output voltage suffered was 11 mV on the analyzed band (-50 °C to 150 °C), inferring a temperature coefficient of 40 ppm/°C. The BGR has a PSRR of 44.6 dB under nomal operational condictions.

Another important result is shown in fig. 7. It shows output voltage variations in response to different supply voltages.

Fig. 7 – Reference voltage in function of supply variations.

We can notice the good stability of the circuit inside of 3-5 V band. Inside of this band was observed a maximum deviation of 12 mV in relation to the nominal conditions of operations.

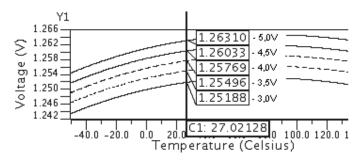

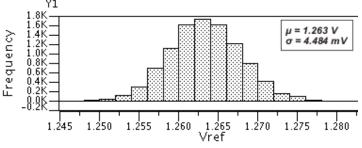

The robustness of the project as analyzed with Monte Carlo simulation. In the Monte Carlo analysis, process and mismatch parameters are modified to verify the yield/limitation of the circuit when submitted to random variations associated to fabrication processes. The simulation was set up to 10000 rounds. The histogram of output voltage is shown in fig. 8.

Fig. 8 – Monte Carlo Simulation

#### 5. Layout

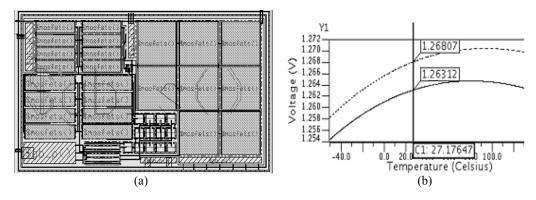

The layout of the circuit is fundamental for a good matching between the components. Some techniques are recommended for layout design, such as: to use components with great dimensions, place the matched components as close as possible and use common-centroid layouts. The final layout is showed in fig. 9 (a). A comparison between simulated and extract results is performed in fig. 9 (b). The total area used by BGR is  $400x230 \ \mu m^2$ .

Fig. 9 - (a) Layout; (b) Comparison between the simulated and extracted results.

#### 6. Conclusions

A bandgap reference circuit was designed and simulated in XFAB-0.6  $\mu$ m CMOS technology. The circuit was especially designed for studying the compromise between matching and area in these topologies. So, a methodology proposed related process parameters and current consumption. As the final result, was obtained bandgap circuit with 1.268 V of output voltage and total consumption of 40  $\mu$ A, as foreseen analytically. The area used is  $400x230~\mu$ m<sup>2</sup>. To validate the design efficiency the circuit will be prototyped.

#### 7. References

- [BRI 07] BRITO, J.P.M; Klimach, H.; Bampi, S. A Design Methodology for Matching Improvement in Bandgap References. Quality Eletronic Design, 2007. ISQED 2007. 8th IEEE International Symposium on, March, San Jose, USA.

- [KIN 05] KINGET, P.R. **Device mismatch and tradeoffs in the design of analog circuits.** Solid-State Circuits, IEEE Journal of, vol.40, no.6pp. 1212-1224, June 2005.

- [PEL 89] PELGROM, M.J.M.; Duinmaijer, A.C.J.; Welbers, A.P.G. Matching properties of MOS transistors. Solid-State Circuits, IEEE Journal of, vol.24, no.5pp. 1433-1439, Oct 1989.

- [RAZ 01] RAZAVI, B. Design of Analog CMOS Integrated Circuits. New York: McGRAW-HILL, 2001.

- [XFA 05] XFAB Semiconductor, **Process Specifications XC06 0.6μm Modular CMOS**, Document PS\_06\_03, 2005.

## Device Characterization of an IBM 0.18 µm Analog Test Chip

#### Giovano da Rosa Camaratta, Eduardo Conrad Jr, Luiz Fernando Ferreira, Fernando Paixão Cortes, Sergio Bampi

{grcamaratta, econradjr, lfferreira, fpcortes, bampi}@inf.ufrgs.br

#### Federal University of Rio Grande do Sul (UFRGS) - Informatics Institute

Postal Code: 15.064 - CEP: 91.501-970 - Porto Alegre - Brazil

#### Abstract

The design of an analog circuit depends on several factors such as good device modeling and technology characterization. In this context, in order to validate the design methodology and the electrical models of a target technology, electrical characterizations based on measurements are necessary. This paper presents the main modules and the characterization of a test chip developed with several RF blocks, oscillators and test devices. The chip was prototyped in IBM 0.18µm CMOS technology process through a MPW service. Preliminary measurements of the ring oscillator and test vehicles will also be presented.

#### 1. Introduction

The development of ultra-scaled VLSI technologies, coupled with the demand for more signal processing integrated in a single chip, has set the trend for integrating analog circuits in digital CMOS technologies below 90 nm feature sizes.

Several analog circuit blocks were designed using a full-custom design methodology based on the  $g_m/I_D$  characteristics, the same methodology that was used in previous works [COR 03]. In the first results, the technology characteristics and circuits performance were obtained with electrical simulations using the foundry-supplied typical BSIM3v3 model parameters for the target technology IBM 0.18 $\mu$ m CMOS technology.

In order to validate the design methodology and the electrical models, electrical characterizations based on measurements are necessary. Thus, a test chip was prototyped in IBM 0.18µm CMOS technology process and 10 not encapsulated chips and 5 encapsulated (64-pin QFN package) have been measured. The objective here is to use the electrical measurements to perform characterization to fine tune the basic design curves and validate the blocks performance.

#### 2. Test Chip Structures

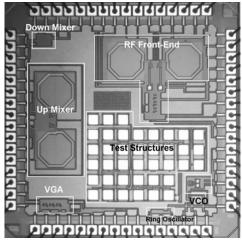

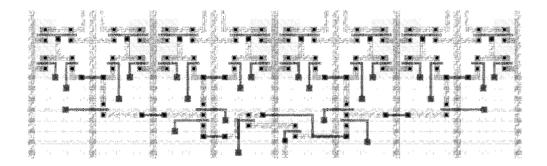

A test chip with the designed blocks and test vehicles in IBM 0.18µm CMOS technology was developed to characterize the design through electrical measurements. The chip microphotography is shown in Fig. 1 and the area of each block is shown in Tab. 1. Each block that composes the test chip is briefly described as follows.

There are 6 RF analog building blocks implemented: a complete variable gain front-end architecture, an up-conversion mixer, a down-conversion mixer, a variable gain amplifier (VGA) [COR 08] and a voltage-controlled oscillator (VCO) using a full-custom design methodology based on the  $g_m/I_D$  characteristics [PAU 07] and a ring oscillator. All the design optimizes both speed and the power consumption, as well as reasonable sensitivity and gain are achieved.

Fig. 1 - Chip die microphotography.

Tab. 1 - System chip area breakdown.

| Block                         | Area (mm²) |

|-------------------------------|------------|

| Up Mixer FI=1.4GHz            | 0.7100     |

| Down Mixer 1.4GHz to 40MHz    | 0.0210     |

| VGA (variable gain amplifier) | 0.0350     |

| Front-End                     | 0.7700     |

| VCO                           | 0.0220     |

| Ring Oscillator               | 0.0073     |

| Test Structures               | 1.2480     |

| Pad Ring                      | 1.7600     |

| Unused Space                  | 2.2260     |

| Total Area                    | 6.8000     |

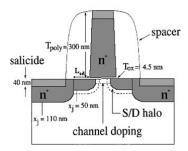

Several test structures was designed in order to allow the extraction of the transistors parameters applicable to all operation regions and all device sizes. The test structures inside the test chip include long ( $L=10\mu m$ ), short ( $L=0.18\mu m$ ), wide ( $W=10\mu m$ ) and narrow ( $W=0.22\mu m$ ) channel transistors. Other geometries are also presented, such as series-parallel associations of transistors (TAT's) of different sizes and shapes [GIR 03].

These structures will be used to characterize the behavior of the drain current, gate transconductance, output conductance, noise and intrinsic frequency in terms of geometry, association of unit transistors and layout strategies. The test structures will be measured through microprobes, so we used micro-pads to access the structures terminals (the PAD's, which were obtained from the IBM 0.18 µm technology library).

The chip microphotography, as shown in Fig. 1, has a total area (including 64 pads) of 6.8 mm<sup>2</sup>. Most of the chip area is occupied by micro-pads, in order to access the device terminals for measurements. The area of each block is shown in Tab. 1.

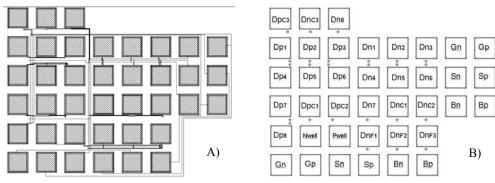

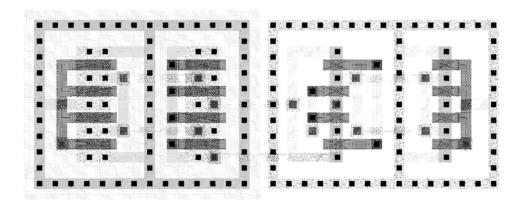

Fig. 2a shows the micro-pads layout prototyped and Fig. 2b presents the micro-pads configuration and transistor location in order to access the structure terminals for testing and measurements. The test chip was fabricated containing a few equivalent composite transistors formed by different associations in 0.18μm CMOS technology composed by unit transistors of equal size. These associations and a reference transistor (a single transistor showing the same W/L relation as a functional reference) are used to achieve by comparative measuring the analog behavior [GIR 03]. Fig. 3a shows an electrical composition of the prototyped TAT associations and the Fig. 3b the PMOS and NMOS TAT layout example.

Fig. 2 – (A) Micro-pads layout and (B) Micropads configuration and transistor location.

Fig. 3 – (A) Electrical configuration of the prototyped TAT's and (B) NMOS and PMOS layout of C1 TAT.

#### 3. Test Characterization Procedure

The test and characterization procedure will follow two main steps. The first step is the characterization of the target process. Using a parameter analyzer and a microprobe station the basic DC measurements was obtained, such as  $Id \times Vd$ ,  $Id \times Vg$  and  $Id \times Vs$ . With these curves many important parameters can be obtained.

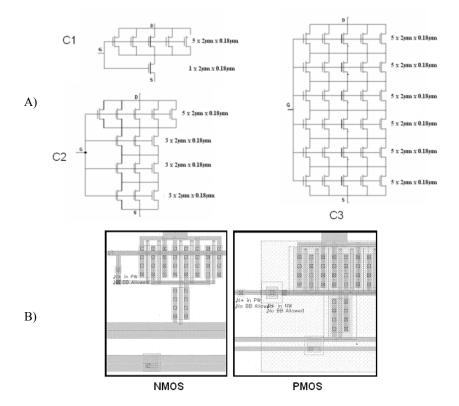

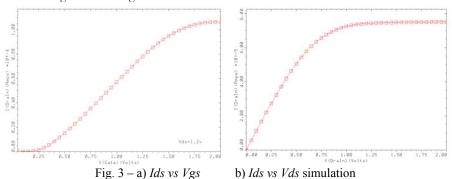

Therefore, the process in use can be fully characterized and the parameters of CMOS simulation models (such as ACM and EKV models) can be obtained. This can be used to fine tune the basic design curves and validate the designed blocks performance. Drain current, gate transconductance, output conductance and noise can be obtained direct from the MOS transistors structures measurements. The maximum frequency for this target process can also be obtained, using the Ring Oscillator structure. Fig. 4 shows some preliminary results for the MOS transistors characterization.

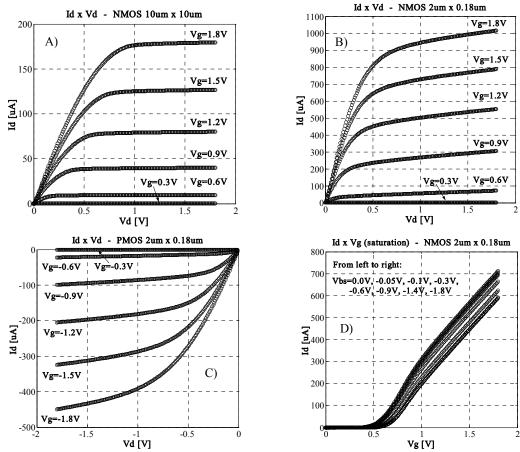

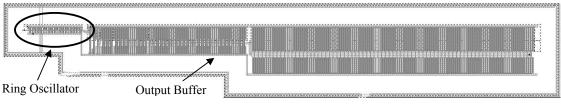

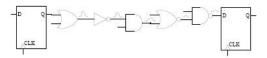

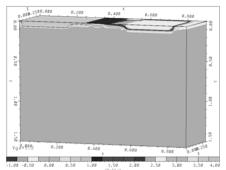

The next step is the fully characterization and validation of each block. In order to verify the gate delay for this process, a ring oscillator was designed and characterized. To verify the resulting average delay time a 19 stage ring oscillator circuit was implemented. The final layout is presented in the Fig.5 and the transistor sizes in the ring oscillator are  $Wp = 0.6\mu m$ ,  $Wn = 0.4\mu m$  and  $Ln = Lp = 0.18\mu m$ .

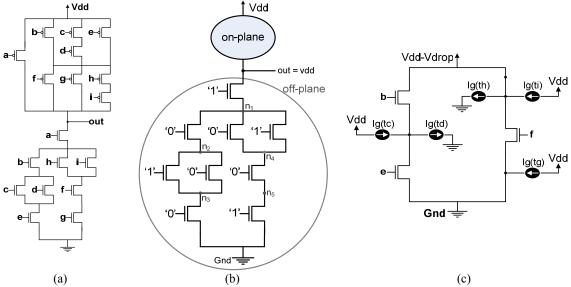

We measured at a typical power supply voltage ( $\pm$  1.8V) the oscillation frequency at about of 630 MHz, resulting in an average gate delay of 41.8ps. Fig. 6a illustrates the oscillation frequency dependency of the power supply and Fig. 6b the average delay versus supply voltage. These results were obtained using a spectrum analyzer through measurement of five samples.

Fig. 4 – (A) Id vs. Vd measured curves for a single NMOS Transistor 10μm x 10μm; (B) Id vs. Vd measured curves for a single NMOS Transistor 2μm x 0.18μm; (C) Id vs. Vd measured curves for a single PMOS Transistor 2μm x 0.18μm and (D) Id vs. Vg measured curves for a single NMOS Transistor 2μm x 0.18μm.

Fig. 5 – Ring Oscillator final layout.

Fig. 6 - Ring Oscillator results: (A) Frequency vs. Supply Voltage and (B) Delay vs. Supply Voltage.

#### 4. Conclusions and Future Work

Electrical characterizations based on measurements are fundamental for the complete analysis of an analog integrated circuit. Only measurements can determine the real circuit functionality. The prototyped test chip is currently under testing, and preliminary measurements of the designed blocks and test vehicles were presented, showing good results performance. As future work, we intend to perform a fully characterization and modeling optimization through electrical measurements to fine tune the basic design curves and validate the blocks performance.

#### 5. Acknowledgements

The support of FAURGS, FINEP, CNPq and CAPES Brazilian agencies with scholarships and PDI-TI Program grant are gratefully acknowledged.

#### 6. References

- [COR 03] CORTES, Fernando Paixão; FABRIS, Eric; BAMPI, Sergio. Applying the g<sub>m</sub>/I<sub>D</sub> Method in the Analysis and Design of a Miller Amplifier, a Comparator and a Gm-C Band-Pass Filter. IFIP VLSI Soc 2003: Darmstadt, Germany, December 2003.

- [COR 08] CORTES, Fernando Paixão; BAMPI, Sergio. Analysis, Design and Implementation of Baseband and RF Blocks Suitable for a Multi-Band Analog Interface for CMOS SOCs. PHD Thesis, PGMICRO – UFRGS, Porto Alegre, RS, 2008.

- [GIR 03] GIRARDI, Alessandro; BAMPI, Sergio. LIT An Automatic Layout Generation Tool for Trapezoidal Association of Transistors for Basic Analog Building Blocks. In: Design, Automation and Test in Europe 2003 - DATE'03. Munich, Germany, March 2003.

- [GIR 03] GIRARDI, Alessandro; CORTES, Fernando Paixão; BAMPI, Sergio. **Analog IC Modules Design Using Trapezoidal Association of MOS Transistors in 0.35µm Technology.** In: 16<sup>th</sup> Symposium on Integrated Circuits and Systems Design (CHIP IN SAMPA), SBCCI 2003. Proceedings. São Paulo, Brazil, September 2003. 311-316 p.

- [PAU 07] PAULA, Luciano S. de; Fabris, E., Bampi, S. A High Swing Low Power CMOS Differential Voltage-Controlled Ring Oscillator. In: 14th IEEE International Conference on Electronics, Circuits and Systems ICECS 2007. December, 2007.

# Accurate Method for Subthreshold and Gate Leakage Current Estimation in CMOS Complex Gates

<sup>1</sup>P. F. Butzen, <sup>1</sup>L. S. da Rosa Jr, <sup>1</sup>E. J. D. Chiappetta Filho, <sup>1</sup>D. S. Moura, <sup>2</sup>A. I. Reis, <sup>1</sup>R. P. Ribas

{pbutzen, leomarjr, ejdcfilho, dsmoura, rpribas}@inf.ufrgs.br, are@nangate.com

<sup>1</sup>Instituto de Informática – UFRGS, Porto Alegre, RS, Brazil <sup>2</sup>Nangate Inc., Menlo Park, CA, USA

#### Abstract

This paper proposes a new method to estimate static power dissipation in digital circuits by evaluating simultaneously subthreshold and gate oxide leakage currents. The estimation method is performed over logic cells, including CMOS complex gates with multi-level series-parallel devices. Experimental results have been carried out on different fabrications processes, and good correlation with  $HSPICE^{TM}$  simulator was obtained. The algorithm presents a speed up of 80x when compared to  $HSPICE^{TM}$ .

#### 1. Introduction

Static power consumption is nowadays a crucial design parameter in digital circuits due to emergent mobile products and leakage current effects. Different leakage mechanisms have been discussed and modeled in literature [ROY 03]. The threshold voltage scaling increases subthreshold current exponentially. The gate oxide tunneling also appeared in sub-100nm as a result of the drastic scaling down of gate oxide thickness, although high-k dielectric are being considered as an efficient solution to overcome such drawback [ITR04].

To face this new challenge, a great effort has been done in developing models and estimators for design support. The 'stack effect' observed with off-transistor (i.e., devices which are turned off) in series arrangement is quite important for subthreshold current prediction [GU 96]. Differently from subthreshold leakage, gate oxide tunneling currents are observed in both on- and off-devices, according to the transistor biasing [RAO 03]. Moreover, on-transistors in off-networks are usually considered by authors as ideal short-circuits in terms of subthreshold current prediction [YAN 05], however this can lead to inaccuracies [BUT 07].

Furthermore, the interaction among leakage mechanisms cannot be ignored in the analysis of static consumption. It was firstly calculated by Mukhopadhyay et al. [MUK 03], and a numerical solver, based on Matlab<sup>TM</sup>, has been developed to evaluate leakage in simple logic gates by solving the Kirchoff's Current Law (KCL) at intermediate nodes, through the use of Sum of Current Source (SCS) transistor model.

In [LEE 03], Lee et al. pointed out the importance and complexity of subthreshold and gate oxide leakage simultaneous analysis, but dealing it through the use of look-up tables composed by SPICE pre-characterized values for a set of distinct transistor biasing. In that work, series-parallel transistor structures are mentioned for only maximum two levels of logic depth, for instance AOI and OAI gates, replacing parallel non-conducting transistor by a single device of equivalent size. It has been already demonstrated in [BUT 07] to be unsuitable for complex gate leakage evaluation.

The particular case of a 3-input NAND gate with the input state where only the device in the middle of the NMOS stack is conducting was discussed in [LEE 03] and [RAO 04]. In the first one, individual leakage results from SPICE simulation. In [RAH 04], the analytical method presented considers the internal nodes, in such biasing condition, quite closed to the power supply potential and the gate oxide leakage value is simply neglected. Moreover, the backward gate leakage current in non-conducting NMOS transistor placed other than on the top of the stack is calculated by considering source-gate voltage equals to power supply voltage minus the device threshold voltage. It is not true for devices placed in different positions in a more representative complex gate, resulting in inaccurate analysis.

No analytical model related to the interaction of leakage currents for multi-level series-parallel complex gates has been found in the literature. The main contribution of this work is to provide a straightforward and accurate method for fast prediction of static power dissipation by interacting different leakage mechanisms in CMOS complex gates. Multi-level series-parallel (SP) device arrangements are considered. An algorithm based on current-source association is proposed to calculate the voltage at internal cell nodes, according to the topology analysis. This avoids the adoption of more complex nonlinear equation solvers [MUK 03].

## 2. Proposed Estimation Method

The subthreshold current is usually modeled by the equation [SHE 87]:

$$I_{S} = I_{0}We^{\frac{V_{gs} - (V_{t0} - \eta V_{ds} - \gamma V_{bs})}{nV_{T}}} \left[ 1 - e^{\frac{-V_{ds}}{V_{T}}} \right]$$

(1)

where  $I_0 = \frac{\mu_0 C_{ox} V_T^2 e^{1.8}}{L}$  and  $V_T = \frac{kT}{q}$ .  $V_{gs}$ ,  $V_{ds}$  and  $V_{bs}$  are the gate-, drain- and bulk-to-source voltages of the

transistor, respectively.  $V_{t0}$  is the zero bias threshold voltage, while W and L are the effective transistor width and length, respectively.  $\gamma$  is the body effect coefficient and  $\eta$  is the DIBL coefficient.  $C_{ox}$  is the gate oxide capacitance,  $\mu_0$  is the mobility and n is the subthreshold swing coefficient.

The gate oxide leakage, in turn, is modeled by the following equation [ROY 03]:

$$I_{gate} = W.L.A \left(\frac{V_{ox}}{t_{ox}}\right)^{2} \exp \left(\frac{-B\left(1 - \left(1 - \frac{V_{ox}}{\phi_{ox}}\right)^{3/2}\right)}{\frac{V_{ox}}{t_{ox}}}\right)$$

(2)

where  $A=q^3/16\pi^2h\phi_{ox}$ ,  $B=4\pi\sqrt{2m_{ox}}\phi_{ox}^{3/2}/3hq$ , W and L are the effective transistor width and length, respectively,  $m_{ox}$  is the tunneling particle effective mass,  $\phi_{ox}$  is the tunneling barrier height,  $V_{ox}$  is the potential drop across the gate oxide,  $t_{ox}$  is the oxide thickness, h is  $1/2\pi$  times Planck's constant and q is the electron charge.

To the purpose of this work, whose goal is to estimate the total leakage current in complex CMOS gates, both equations (1) and (2) can be simplified to the following equations (3) and (4), respectively:

$$I_S = I_{S0}We^{\frac{V_{gs} + \eta V_{ds} + \mathcal{W}_{bs}}{nV_T}} \left[ 1 - e^{\frac{-V_{ds}}{V_T}} \right]$$

$$(3)$$

where

$$I_{S0} = \frac{\mu_0 C_{ox} V_T^2 e^{1.8 \frac{V_{t0}}{nV_T}}}{L}$$

, and

$$I_{g} = I_{g0}.W.e^{\frac{-K}{|V_{ox}|}}$$

(4)

where  $I_{g0}$  represents the gate leakage current for  $V_{ox} = V_{dd}$ , and K is a calibration constant. Due to the transistor bias state dependence, the proposed model considers the gate leakage currents for transistor turned ON  $(I_{g\_ON})$  and turned OFF  $(I_{g\_OFF})$ . The parameters  $I_{S0}$ ,  $I_{g\_OFF}$ , K,  $\eta$ , and  $\gamma$  are extracted through electrical simulation.

#### 2.1. Cell Leakage Estimation Heuristic

In order to calculate each leakage current component, the voltage at cell internal nodes must be known. However, every current contributes on that by interacting each other. The proposed algorithm consists in three basic steps:

(1) On- and off-plane identification and off-network extraction – It consists in identifying the state of conduction of the logic planes (called here as on- and off-planes), for a certain input state condition. Notice that, in on-planes, the subthreshold leakage mechanism is not observed, while the gate oxide leakage is verified at switched-on transistors. Moreover, all nodes at the pull-up PMOS or pull-down NMOS conducting plane attain the power supply voltage (Vdd) or ground voltage (gnd), respectively.

The off-network is extracted from the off-plane by evaluating the conducting of devices in this plane. Ondevices have their source and drain terminals short-circuited, and a current source representing the gate oxide current contribution is associated to such node. Note that, nodes short-circuited by on-transistors can eventually remove other devices, but again the contribution of these devices must be represented by current sources at the node in analysis.

(2) Internal node voltages calculation – The unknown internal node voltages have to be determined. For that, these nodes are treated in a sequential way, calculating firstly the nodes nearest to the cell output terminal, while the other unknown nodes are temporarily considered at the reference *Vdd* or *gnd*, according to the plane type. This procedure avoids the use of complex and time consuming nonlinear solvers, like Matlab<sup>TM</sup> and SPICE, without significant lost in accuracy.

The currents from all devices connected to a certain node in evaluation are then associated using the KCL principle, including also the current sources added when replacing the removed devices, mentioned before. Considering this procedure, the evaluated voltage represents in fact the drain-to-source voltage of the transistors connected at the supply reference. To compute the unknown internal nodes values, a roughback procedure from supply reference will compute the drain-to-source voltage of each transistor.

(3) Total leakage current estimation – Once all internal node voltages have been determined, the leakage currents are then estimated taking into account these voltage values. To account the total cell leakage, the subthreshold currents of the devices connected to the ground terminal (power supply terminal for PMOS offplane) are summed, as well as the gate oxide leakage resulted from off-devices in the off-network. On-devices

connected to ground terminal in the off-plane and removed during the generation of the off-network also contribute to the final total leakage through the on-gate leakage. Finally, the gate leakage of the on-devices in the on-plane must be added to the final value

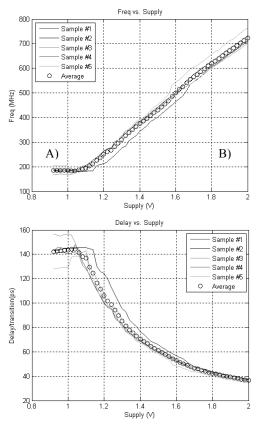

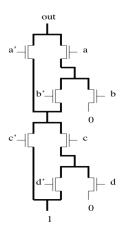

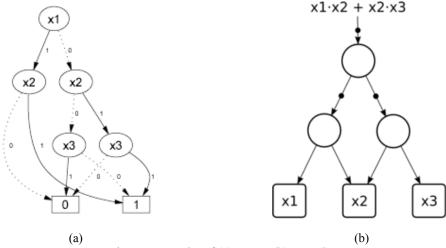

#### 2.2. Case Study: Method Demonstration

To illustrate the procedure described in the previous sub-section, the complex gate depicted in Fig. 1a is considered. Taking into account the input vector [a,b,c,d,e,f,g,h,i] = [1,0,1,0,0,0,1,0,1], as shown in Fig. 1b, the pull-up PMOS plane represents the conducting one, while the pull-down NMOS plane is the off-plane, it means the output node presents the power supply voltage Vdd. The off-network extracted from the off-plane is shown in Fig. 1c. For this particular example, some conditions discussed before can be identified:

- (a) the NMOS transistor with 'a' input ('ta'), placed at the top of the off-plane, is turned on, resulting in a voltage drop over it;

- (b) the NMOS transistor 'tc' is short-circuited. It leads to the stack of two off-devices separate by an ontransistor, as pointed out in other works as a special case [LEE 03]. Both transistor 'tc' and 'td' are replaced by source currents;

- (c) the NMOS transistor 'ti' is short-circuited. 'ti' and 'th' are replaced by source currents and 'tf' is connected to the top terminal;

- (d) the transistor 'tg' is also short-circuited and replaced by a current source.

Fig. 1 – Complex CMOS logic gate: (a) original topology, (b) indication of steady state condition, (c) off-network from the off-plane.

In this case study only one node in the off-network is unknown, corresponding to the original 'n2' and 'n3' joined. To calculate it, the subthershold current from devices 'tb' and 'te', as well as the gate oxide leakages from the off-devices 'tb', 'td' and 'te' and the on-device 'tc' are associated according to their direction.

The total cell leakage current is then estimated by summing all current going out from the logic gate or, in other words, the currents flowing to the ground potential. It includes the gate leakage in the on-PMOS transistors and the off-NMOS ones, whose gate terminal is <u>connected</u> to low logic level. Moreover, the subthreshold current of the transistors connected to the *gnd* terminal, as well as the gate current of the on-NMOS 'tg' connected to the same ground node must also be added to the final value.

#### 3. Experimental Results

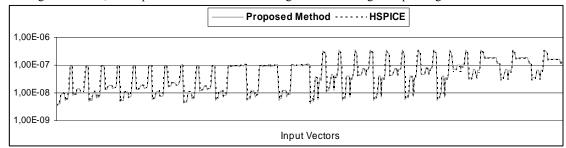

To validate the proposed leakage estimation method in CMOS technology, the results obtained analytically were correlated with HSPICE<sup>TM</sup> simulation data, considering 65nm and 45nm CMOS Predictive Technology Model (PTM) process parameters [PTM 08].

First of all, the complex gate presented in Fig. 1a was evaluated to all input combinations, as shown in Fig. 2. The method was also evaluated at circuit level, taking into account ISCAS85 benchmark circuits [BRG 85] mapped with GenLib\_44-6 library. The steady state of each internal cell in the circuit is pre-evaluated for a certain primary input vector. The leakage current in the cells is then calculated individually, and summed for the total current estimation. Results obtained at circuit level are shown in Tab. 1. The results present a good correlation to HSPICE<sup>TM</sup> simulation and a speed up of 80X.

The major contributor for the prediction error has been identified to be the switched-on devices voltage drop present in the off-plane. On-devices have been treated by other authors as ideal short-circuits. Besides it has significant impact in the leakage current estimation when they are placed at the top of the off-plane, it also

presents different values according to the number of off-stacked-transistor bellow that. Although it suggests a small voltage difference, the impact in the subthreshold and gate oxide leakages is quite significant.

Fig. 2 – Leakage current in the logic gate from Fig. 1a using 45nm PTM process, for all 512 input combinations.

| Tab 1 - Total | leakage current es | timation for ISC. | AS85 benchmark | circuits [BRG 85]. |

|---------------|--------------------|-------------------|----------------|--------------------|

|             | P      | TM 65nm              |       |        | PTM 45nm            |       |

|-------------|--------|----------------------|-------|--------|---------------------|-------|

| I_leak (μA) | Method | HSPICE <sup>TM</sup> | Error | Method | HSPICE <sup>T</sup> | Error |

| C432        | 11.8   | 11.3                 | 4.4%  | 22.0   | 20.9                | 5.3%  |

| C499        | 37.2   | 35.6                 | 4.5%  | 69.8   | 65.6                | 6.4%  |

| C888        | 19.8   | 18.8                 | 5.3%  | 36.3   | 34.2                | 6.1%  |

| C1355       | 39.9   | 38.0                 | 5.0%  | 73.6   | 69.1                | 6.5%  |

| C1908       | 30.3   | 29.0                 | 4.5%  | 54.9   | 51.5                | 6.6%  |

| C3540       | 65.3   | 61.9                 | 5.5%  | 122    | 114                 | 7.0%  |

| C6288       | 200    | 191                  | 4.7%  | 370    | 350                 | 5.7%  |

#### 4. Conclusions

A new leakage current estimation method for CMOS circuits was presented, providing clear improvement in the state-of-the-art. Subthreshold and gate oxide leakages are both considered in the analysis by interacting such mechanisms. The proposed heuristic defines a sequential procedure, making some assumptions which simplify the current source equations calculation, without penalty in accuracy. The main factor of difference to HSPICE<sup>TM</sup> simulation data, taken here as the golden reference, is the variation in the drain-to-source voltage of switched-on transistors, usually ignored by other authors which consider it as an ideal short-circuit. Finally, the estimation method computation is significantly faster when compared to electrical simulation.

#### 5. Referências

- [BRG 85] BRGLEZ, F. et al. A Neutral Netlist of 10 Combinatorial Benchmark Circuits. ISCAS 1985, pp. 695-98.

- [BUT 07] BUTZEN, P. F. Butzen et al. Modeling and Estimating Leakage Current in Series-Parallel CMOS Networks. GLSVLSI 2007, pp. 269-274.

- [GU 96] GU, R. X. et al. **Power Distribution Analysis and Optimization of Deep Submicron CMOS Digital Circuit.** IEEE J. Solid-State Circuits, vol.31, no.5, May 1996, pp.707-713.

- [ITR 04] **International Technology Roadmap for Semiconductors**, 2004 Edition. Available at http://public.itrs.net.

- [LEE 03] LEE, D. et al. Simultaneous Subthreshold and Gate-Oxide Tunneling Leakage Current Analysis in Nanometer CMOS Design. ISQED 2003, pp. 287-292.

- [MUK 03] MUKHOPADHYAY, S. et al. Accurate Estimation of Total Leakage in Scaled CMOS Logic Circuits Based on Compact Current Modeling. DAC 2003, pp. 169-174.

- [PTM 08] Berkeley Predictive Technology Model. Available at http://www-device.eecs.berkeley.edu/~ptm.

- [RAH 04] RAHMAN, H. et al. A Leakage Estimation and Reduction Technique for Scaled CMOS Logic Circuits Considering Gate-Leakage. ISCAS 2004, vol.2, pp. 297-300.

- [RAO 03] RAO, R. M. et al. Efficient Technique for Gate Leakage Estimation. ISLPED 2003pp. 100-103.

- [RAS 07] RASTOGI, A. et al. An Efficient Technique for Leakage Current Estimation in Sub 65nm Scaled CMOS Circuits Based on Loading Effect. IEEE VLSID 2007, pp. 583-588.

- [ROY 03] ROY, K. et al. Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits. Proceedings IEEE, vol. 91, no. 2, Feb. 2003, pp. 302-327.

- [SHE 87] SHEU, B. J. et al. BSIM: Berkeley Short-Channel IGFET Model for MOS Transistors. IEEE J. Solid-State Circuits, vol. SC-22, no. 4, Aug. 1987, pp. 558-566.

- [YAN 05] YANG, S. et al. Accurate Stacking Effect Macro-modeling of Leakage Power in Sub-100nm Circuits. Proc. Int. Conf. on VLSI Design, Jan. 2005, pp. 165-170.

# A 65nm CMOS Analog Processor for Mobile Terminals Software Radio Front End

<sup>1</sup>François Rivet, <sup>1</sup>Yann Deval, <sup>1</sup>Domnique Dallet, <sup>1</sup>Jean-Baptiste Begueret, <sup>2</sup>Didier Belot, <sup>2</sup>Philippe Cathelin

francois.rivet@ims-bordeaux.fr, didier.belot@st.com

<sup>1</sup>IMS Laboratory, University of Bordeaux, Talence, France <sup>2</sup> STMicroelectronics R&D, Crolles, France

#### **Abstract**

The forth generation of mobile terminals is the place of multimedia convergence. Audio, video and data are told to be broadcast on the same device. Microelectronics industry is challenging to integrate all these applications. The Software Radio concept is one of the key to overcome technological bottleneck implied by mobile devices constraints. This paper presents the architecture and the design of a 65nm CMOS analog component in the RF receiving chain. Behavioural and post-layout simulations are depicted to validate the design of a RF analog processor.

#### 1. Introduction

The Software Radio (SR) concept aims at bringing closer the antenna to a reprogrammable component in the RF receiving chain. Researches are more and more concentred on this topic since the last decade [MIT 95] because of the emergence of various RF standards and the need to broadcast them all together. That is why telecommunications industry is looking for solutions to integrate low cost, low power chips in mobile devices to answer this problematic. Multi-standard, multi-functional systems were studied using the concept of Software Defined Radio [ABI 06]. Whereas this concept allows handling several radio communication standards, SDR architectures are still limited to a few defined RF standards. Cognitive Radio (CR) emergence asked for more flexible architectures, like Software Radio.

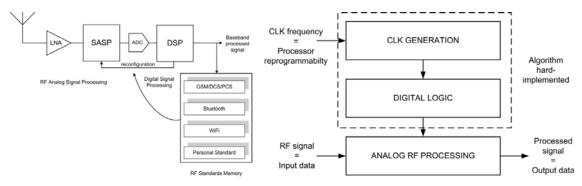

This paper presents a Software Radio processor for mobile terminals. The Software Radio concept is ideally implemented in a receiving chain with an antenna directly connected to an Analog-to-Digital Converter (ADC) which displays the RF digital converted signal to a DSP. Then, the DSP can process digitally any RF signals and thus demodulate any kind of communication standard whatever its frequency, its channel bandwidth, its modulation. Such a system is not feasible according to mobile terminals constraints. The power consumption and the resolution of an ADC at high frequencies are the technological bottleneck. To overcome this problem, it is proposed to design an analog processor which process analogically RF signals at an acceptable power consumption for mobile terminals (Fig. 1). This component is called Sampled Analog Signal Processor (SASP). The analog operations executed by the processor can be done at high frequencies and at low power consumption.

A Processor is a component which implements an algorithm to process data (Fig. 2). The SASP is divided into 2 main parts: one to address the algorithm, one to receive and send data by the mean of a RF signal (Fig. 2). Each part is detailed in the next paragraphs.

Figure 1: A SR receiving chain

Figure 2: Processor Architecture

#### 2. A Sampled Analog Signal Processor

#### 2.1 The Butterfly Algorithm

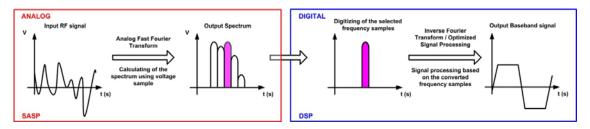

The Sampled Analog Signal Processor implements the algorithm of a Discrete Fourier Transform (DFT) (Fig. 2). It goals at processing the spectrum of any RF signal in a range from 0 GHz to 5 GHz. Once the spectrum processed analogically, it is delivered through voltage sample (Fig. 3). It is just a matter to select the voltage sample representing the spectral envelope of the desired RF signal. Only this selected envelope is converted in digital. The selection of voltage samples participates to the reduction of the working frequency of the ADC. At a constant frequency, the SASP enables to lower the processing speed and the data rate of the ADC and the DSP. Thus, the power consumption is dramatically reduced and a Software Radio architecture can be integrated in a chip destined to mobile terminals.

Figure 3: Processor principle

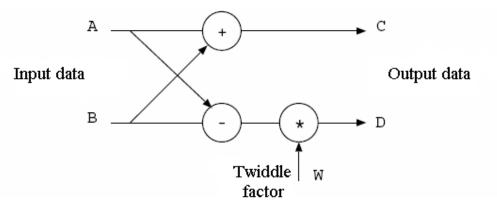

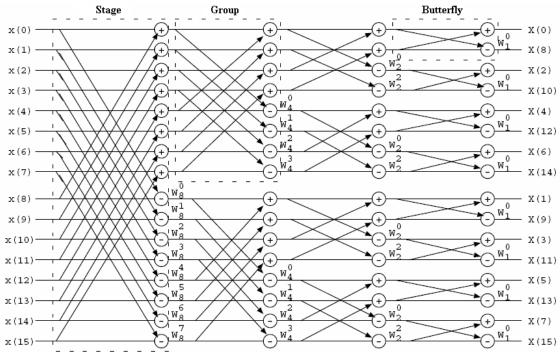

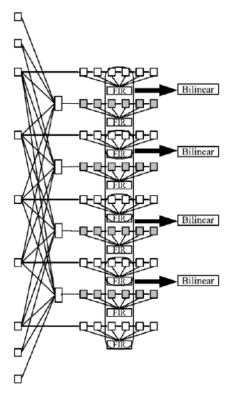

To implement the DFT, a radix-4 Butterfly algorithm is chosen (Fig. 4) [SWA 84]. It is a pipelined FFT. It is composed by n=log<sub>4</sub>(N) generic modules, with N the number of samples taken into account for the FFT processing. Each module is detailed into 3 parts, extracted from the FFT formula [RIV 08]. It is structured by a delay line, a Processing Unit and a delay line feedback. The implementation of these modules is analog and controlled by a digital part [RIV 07].

Here is depicted the example of a 16-sample FFT (Fig. 4). The input vector is x(1..N) and the output vector is x(1..N). The input vector is made of voltage samples, representing the discretized RF signal. The output vector is made of voltage samples, representing the spectrum of the RF signal.

The order of the output voltage is a base-4-reversed order. It means that the base-4 bits are inverted (Fig. 4). It determines the position of expected voltage samples. This order implies a decimation by 4 of the output frequency because 2 neighbor voltage samples X(i) and X(i+1) are thus spaced by  $4^{n-1}$  voltage samples.

Figure 4: 16-sample FFT

Figure 5: An analog implementation of the generic module

#### 2.2 Analog Signal Processing

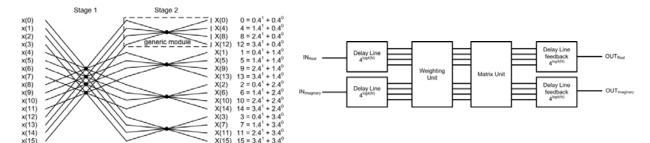

Analog signal processing induces errors based on technological mismatch such as in transistors sizing, current variations and others. The impact of these errors has to be taken into consideration. That is why two major sources of errors are identified in the Processing Unit (PU) composed by the Matrix Unit (MU) and the Weighting Unit (WU) implemented in the generic module (Fig. 5). To evaluate the influence of those errors, the normal law is used as a model for technological matching. Gaussian law is defined by its mean value and its standard deviation. Figure 2 depicts the standard deviation bounded by dynamic of error.

If  $\sigma$  is the standard variation and  $\epsilon$  the induced error (percentage), it is reasonable to say that: -3  $\sigma$  <  $\epsilon$  < 3 $\sigma$  A standard deviation of 0.05 is considered. It implies errors under 15%. Figure 6 exhibits the distortion of a processed signal into 3 modules (named "stage") of a 64-sample FFT. Errors are injected on each part of a stage, then each stage and finally on all the FFT circuit.

Figure 5: The normal law

Figure 6: Distortion observed on a processed RF signal

It is easy to notice that the Processing Unit is the most sensitive part of the circuit. The Weighting Unit is the responsible for error introduction in the PU. The design of this module should be done carefully in order to limit the impact on all other parts of the circuit.

#### 3. Analog Signal Processor Schematics

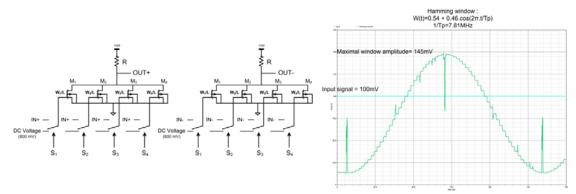

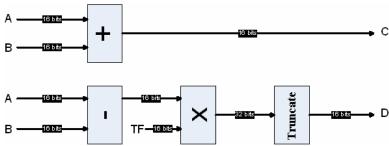

A SASP is designed to process 64 samples (N=64). 3 modules are pipelined. The schematic is ruled by specifications enforced by a differential structure with a dynamic range of 200mV at a working DC voltage of 800mV. The maximal frequency of this SASP is a sampling frequency of 1GHz. It can thus process RF signals from 0 to 500MHz. Analog building blocks are designed using the 65nm CMOS technology from STMicroelectonics to realize the analog basic operations of the processor [RIV 07]. One of them is an analog discrete multiplication of an RF discrete signal with coefficients within the interval [0,1]. It aims at windowing the RF signal with a Hamming window, depicted by the equation  $W(t) = 0.54 + 0.46 \cos(2\pi.t/T_p)$ .

The principle used here is a voltage/current/voltage conversion. Voltage samples are sent on gates of a series of transistors (Fig. 7). The current crossing each transistor is proportional to the input voltage equal to  $V_{gs}$ . A switch network ( $S_x$ ) selects the input voltage of each transistor gate (Fig. 7). The input voltage can be either a voltage sample to be weighted or the DC reference voltage (800mV). The voltage seen at the drain of the transistors is proportional to the sum of the input voltages. The configuration of the switch network determines the coefficient to be applied. Every transistor ( $M_x$ ) has a different size (Fig. 7). It implies that the current crossing each transistor is no more proportional to the input voltage but to the width of the transistor. Switches are controlled by a hard-implemented digital circuit which is synchronized on the SASP main clock. A simulation is depicted with a constant input voltage of 100mV peak to peak (Fig. 8). The Hamming window can be noticed at the ouput, as the multiplication with a constant signal and amplifying the signal by a factor of 1.45.

Figure 7: Analog discrete multiplication circuit

Figure 8: Hamming window simulation

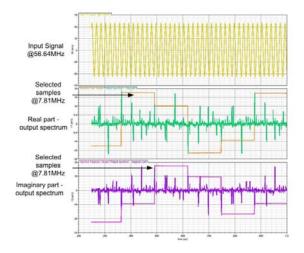

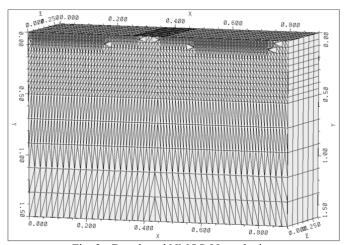

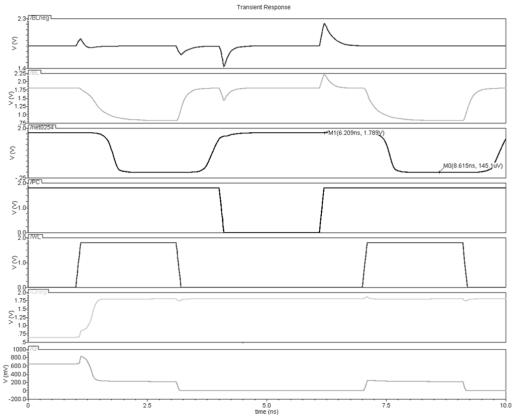

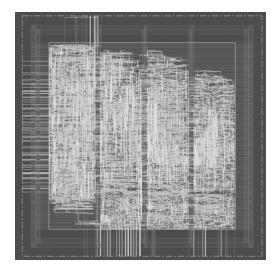

#### 4. Modeling results

A Post Layout Simulation is done to validate the 65nm CMOS technology circuit behavior (Fig. 9). The SASP carries out analog operations on voltage samples of a sine wave with a frequency equal to  $7.25 \cdot f_{\text{sampling}}/64 = 56.64 \text{MHz} \cdot (f_{\text{sampling}})$  is equal to 500 MHz. Only the 7th voltage samples processed by the processor is selected

and displayed. It contains the phase and amplitude information of the input signal. As expected, the spectrum is periodic every 4 processed FFT and output at a low frequency of 500/64=7.81MHz. The whole power consumption is 352mW and the die area is 0,96mm² as shown in a layout view (Fig. 10). An A/D conversion is thus possible at a lower frequency and further versions of the SASP with 4096, 16384, 65536 samples can be envisaged to process RF signals such as GSM or WiFi.

DIGITAL CIRCUIT

ANALOG RF

PROCESSING CIRCUIT

Figure 9: A Post Layout Simulation

Figure 10: SASP Simplified Layout

#### 5. Conclusion

This paper exhibited the principle, behavior simulations, schematics and layout design of a 65nm CMOS analog processor dedicated to RF applications in order to address the concept of Software Radio. It validates the principle of calculation based on analog voltage samples at RF frequencies. The SASP aimed at being part of the solution to access to a fully reconfigurable mobile terminal working on the Cognitive Radio approach in the radio spectrum range from 0 to 5GHz.

#### 6. Reference

- [MIT 95] J. MITOLA. The Software Radio Architecture. In: IEEE Communications Magazine, vol 33, May 1995, pp 26-38.

- [ABI 06] A.A. ABIDI. **Software-defined radio receiver: dream to reality**. In: IEEE Communications Magazine, 2006, pp. 111-118.

- [SWA 84] E. SWARTZLANDER, W. YOUNG, and S. JOSEPH. A radix 4 delay commutator for fast fourier transform processor implementation. In: IEEE Journal of Solid-State Circuits, vol.19, pp. 702-709, Oct. 1984.

- [RIV 08] F. RIVET, Y. DEVAL, D. DALLET, JB. BEGUERET, P. CATHELIN and D. BELOT. Disruptive Receiver Architecture Dedicated To Software Defined Radio. In: IEEE TCAS-II, to be published, April 2008.

- [RIV 07] F. RIVET, Y. DEVAL, D. DALLET, JB. BEGUERET, P. CATHELIN and D. BELOT. A Disruptive Software-Defined Radio Receiver Architecture Based on Sampled Analog Signal Processing. In: Proceedings IEEE RFIC, Honolulu, USA, June 2007, pp 197-200.

| NETWORKS-ON-CHIP |  |

|------------------|--|

|                  |  |

# Functional Test of Networks-on-Chip: Test of Routers

#### <sup>2</sup>Pedro Almeida, <sup>1</sup>Marcelo Lubaszewski, <sup>2</sup>Marcos Hervé, <sup>2</sup>Fernanda Lima Kastensmidt, <sup>2</sup>Érika Cota

{prvalmeida, fglima, erika}@inf.ufrgs.br, luba@ece.ufrgs.br, marcos.barcellos@ufrgs.br

#### <sup>1</sup>Electrical Engineering Department, <sup>2</sup>Computer Science Department Federal University of Rio Grande do Sul, Porto Alegre, Brazil

#### Abstract

In this work, a functional-based test method is presented for the test of Network-on-Chip routers. The proposed approach is scalable to any size of network. Experimental results show that fault coverage can reach up 92.75% of router stuck-at faults, with yet affordable test sequence lengths.

#### 1. Introduction

The advent of system-on-chip (SoC) technology and integration of multiple cores and Network-on-Chip (NoC) on a single die brought new challenges in terms of testability [BEN 02, GEN 07, ANG 06]. Defining an efficient test strategy of such a new kind of system architecture is still a challenge to be overcome by the research community. It is well-known that the test of NoC-based multicore chips is generally divided on the test of cores and on the test of the communication infrastructure (network). The test of cores is usually based on the reuse of the NoC as Test Access Mechanism (TAM) to reduce area overhead and test time [COT 04]. As a result, the testing of the communication infrastructure is essential to guarantee the reliability of the entire system.

This work focuses on the functional testing of the NoC infrastructure. An improved version of a functional-based method originally proposed for the detection of interconnect shorts is used to detect stuck-at faults in the routers. Then, new configurations are used to reach maximum coverage. A functional-based approach is preferred, to reduce NoC re-design costs and to provide at-speed testing. However, scan and BIST-based approaches may be required to enhance both fault coverage and test application time.

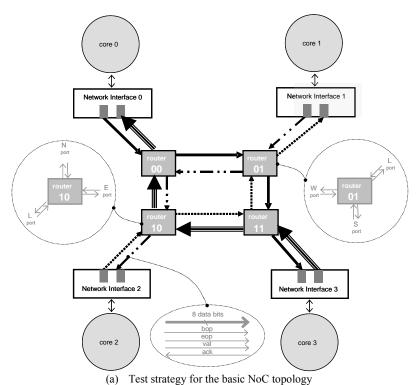

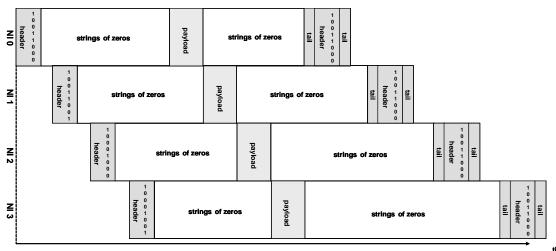

#### 2. Test Strategy

Our test strategy is defined by the following steps:

- 1) the interconnections are tested using an improved version of the functional-based method originally proposed in [COT 04] (many router faults are inherently detected in this step also);

- additional test configurations are applied to the NoC in functional mode, such that the fault coverage

of interconnects and routers is increased to the maximum affordable test application time and network

interface area overhead;

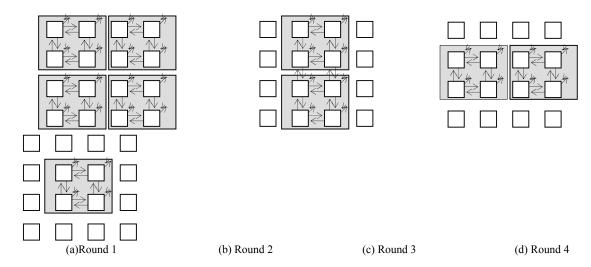

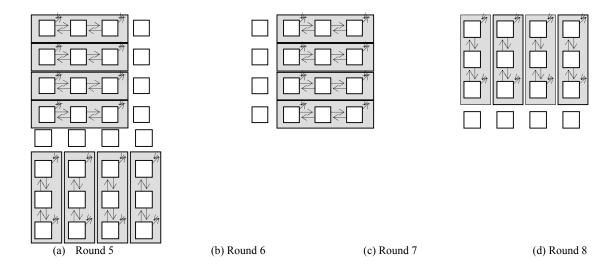

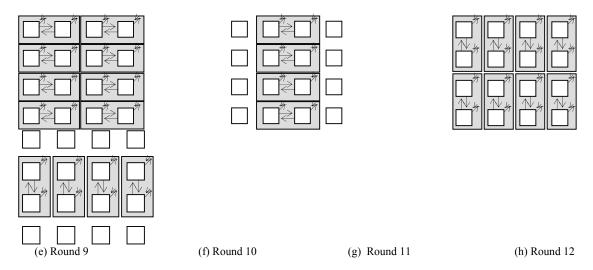

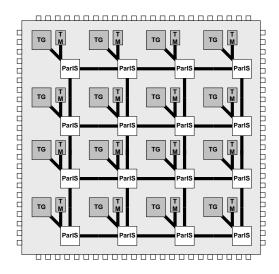

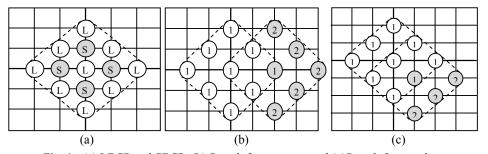

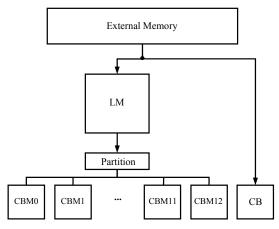

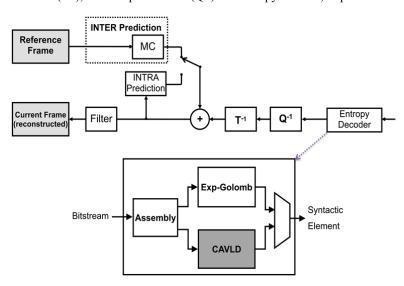

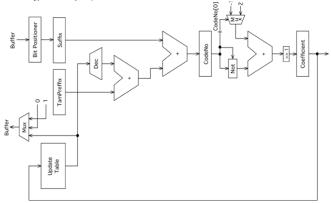

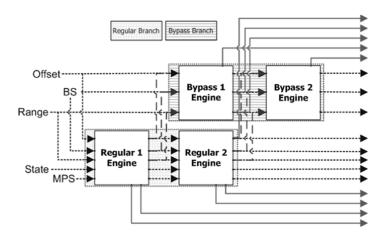

The proposed method consists in detecting stuck-at faults in the routers of a 2x2 NoC by sending packets through the network (fig. 1(a)). To implement this test strategy, test patterns must be applied through and test responses collected from the network interfaces (NIs). The router is a VHDL soft core, parameterized in three dimensions: communication channel width, input buffer depth, and routing information width and was configured with five ports—north (N), south (S), west (W), east (E), and local connection between router and core (L)—a 3-position depth and a 10-bit width input buffer. Each communication channel actually has 12 bits: eight bits for data, two extra wires for framing (stored in the input buffer) called framing bits or beginning of packet (bop) and end of packet (eop) bits, and two signals for the communication handshake between routers (val and ack). After synthesizing the RASoC router according to these parameters, 959 logic stuck-at locations come out, resulting in a model that contains 1,918 faults, including stuck-at 0 and stuck-at 1 faults.