#### EMICRO/SIM 2013

XV Escola de Microeletrônica Sul / 28° Simpósio Sul de Microeletrônica Porto Alegre, 29 de abril a 3 de maio de 2013

# Teste e Caracterização de Circuitos Integrados

Tiago Roberto Balen

tiago.balen@ufrgs.br

Promoção

Apoio

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando a Testabilidade e Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

#### Sumário

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando a Testabilidade e

- Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

#### Avanços da Tecnologia

- Bens de consumo

- · Eletrônica embarcada

- Telecomunicações

- Entretenimento

- Aplicações hospitalares

- Aplicações industriais

- Aplicações militares

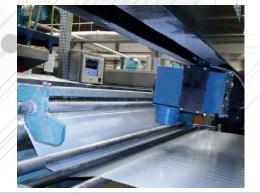

#### Avanços da Microeletrônica

- Aumento da capacidade de integração

- Diminuição das dimensões dos transistores

#### Avanços da Microeletrônica

- Aumento da capacidade de integração

- Diminuição das dimensões dos transistores

- Aumento das frequências de relógio

- Aumenta susceptibilidade e probabilidade de defeitos

- Necessidade de fornecer produtos confiáveis a um custo competitivo

- Exemplos:

- Ind. Automobilística

- Ind. Aeronáutica

- Apl. Biomédicas

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando à Testabilidade e Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

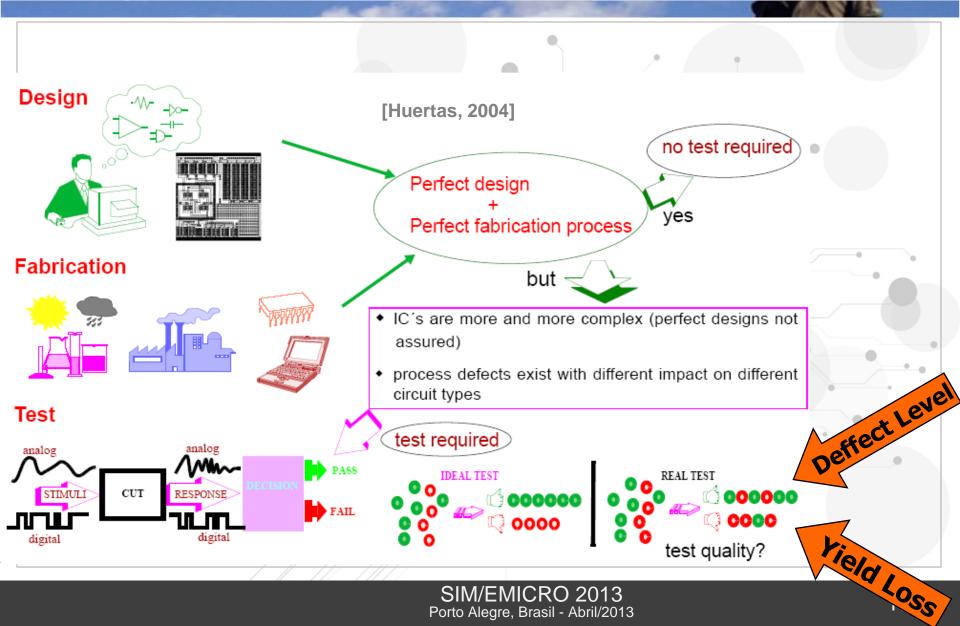

## Definições

- Verificação do bom funcionamento do circuito

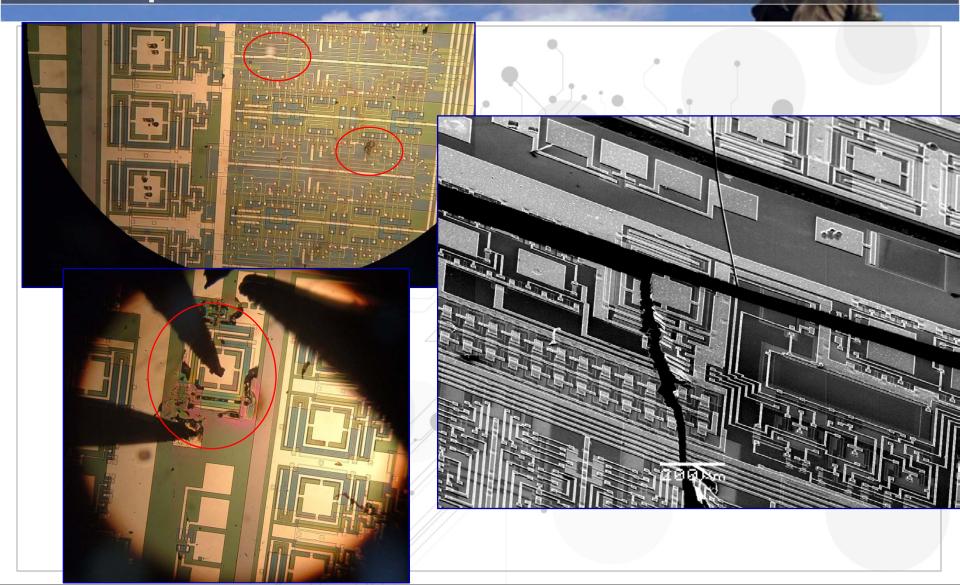

- Defeito: "diferença entre o hardware implementado e o projetado"

- Físico

- Processo: falta de contatos ou vias; parasitas; variações causadas por desalinhamento de máscaras

- <u>Material</u>: quebras no substrato; imperfeições no cristal (silício); impurezas; spot deffects

- Encapsulamento: degradação de contatos, falta de ligação entre PADs e pinos

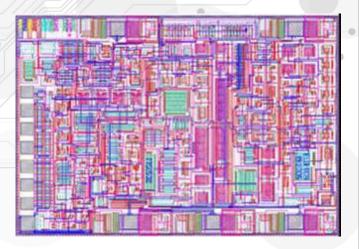

# Processo CMOS

Tabela 1. Defeitos comuns na tecnologia CMOS padrão [7, 8].

| Probabilidade | Defeitos em transistores                                                   | Falhas em interconexões                                              |

|---------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|

| Maior         | Curto entre porta e fonte<br>Curto entre porta e dreno                     | Curto entre linhas de difusão                                        |

| Î             | Circuito aberto no contato de dreno<br>Circuito aberto no contato de fonte | Quebras no cruzamento de linhas<br>de metal e silício polycristalino |

| Menor         | Curto entre porta e substrato<br>Circuito aberto no contato de porta       | Curto entre linhas de metal                                          |

#### Falhas catastróficas x Paramétricas

# Exemplos

## Definições

- Verificação do bom funcionamento do circuito

- Defeito: "diferença entre o hardware implementado e o projetado"

- De projeto:

- violação de regras de projeto,

- simplificação de modelos

- falha na integração de blocos

#### Definições

- o Verificação do bom funcionamento do circuito

- Defeito

Falha: manifestação interna de um defeito ("abstração funcional")

Erro: manifestação externa de uma falha

Uma falha é detectada observando-se um erro causado por ela!

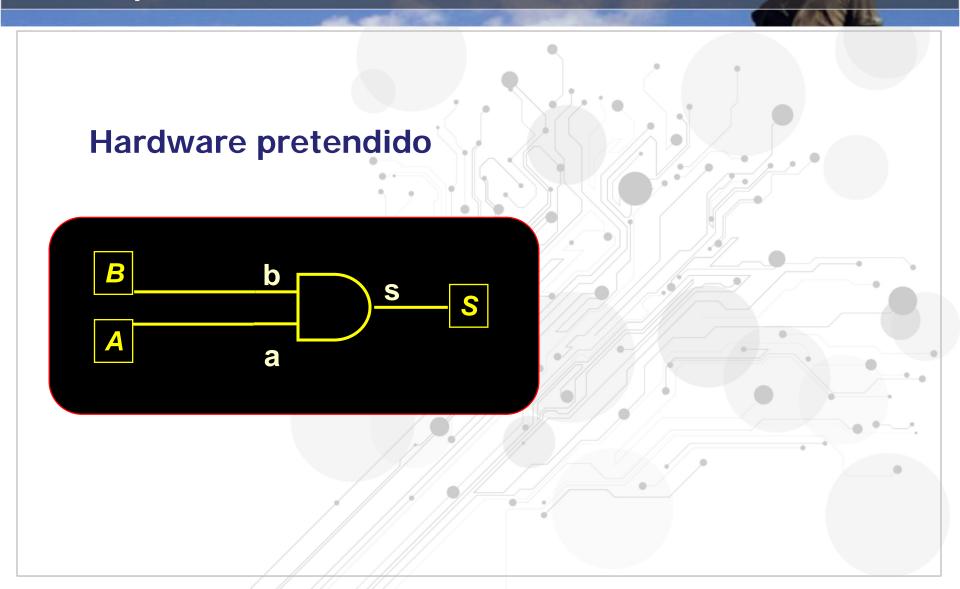

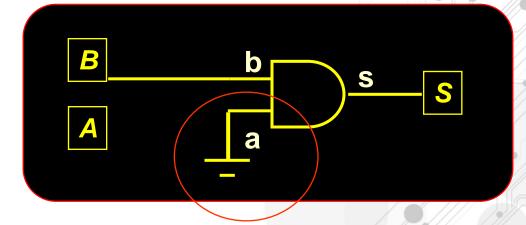

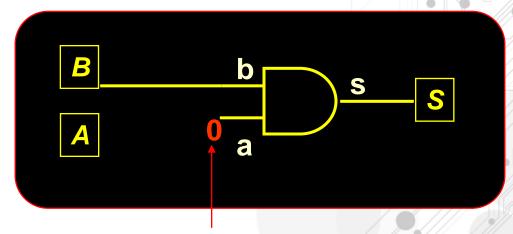

#### Exemplo

# Exemplo

Defeito: entrada "a" conectada ao GND

#### Exemplo

Função de saída modificada:

Função correta: S = A-B

Função resultante: S = 0

Falha: entrada A colada em nível lógico 0

Ocorrerá um erro quando A = B = 1

Valor correto: S = 1

Valor obtido: S = 0

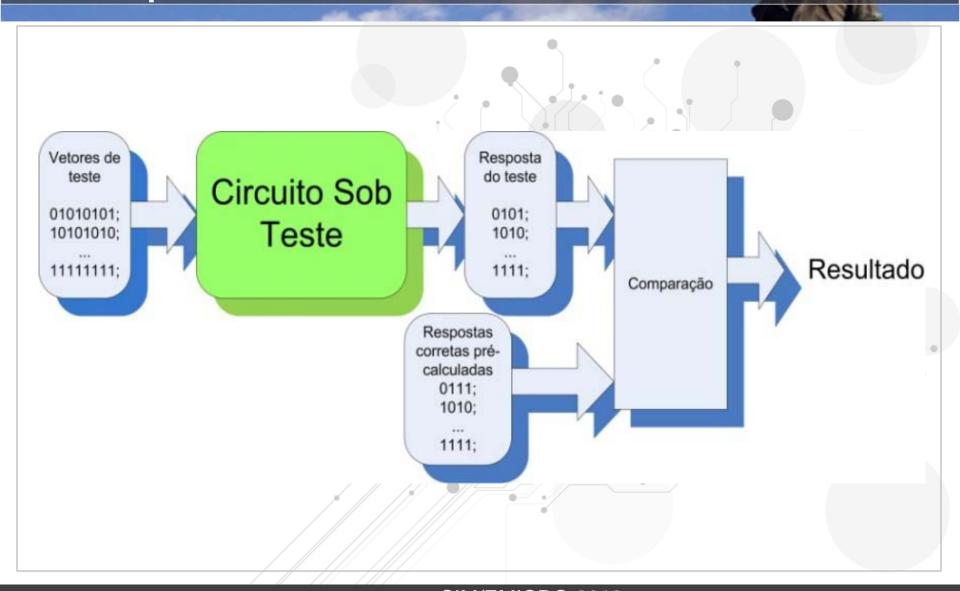

#### Princípio Básico do Teste

#### O Papel do Teste

- Classificar um circuito como Bom ou Falho (Go / NoGo)

- O Circuito Falho: Algo deu errado!

- Especificações

- Projeto

- Processo

- Teste

Diagnóstico

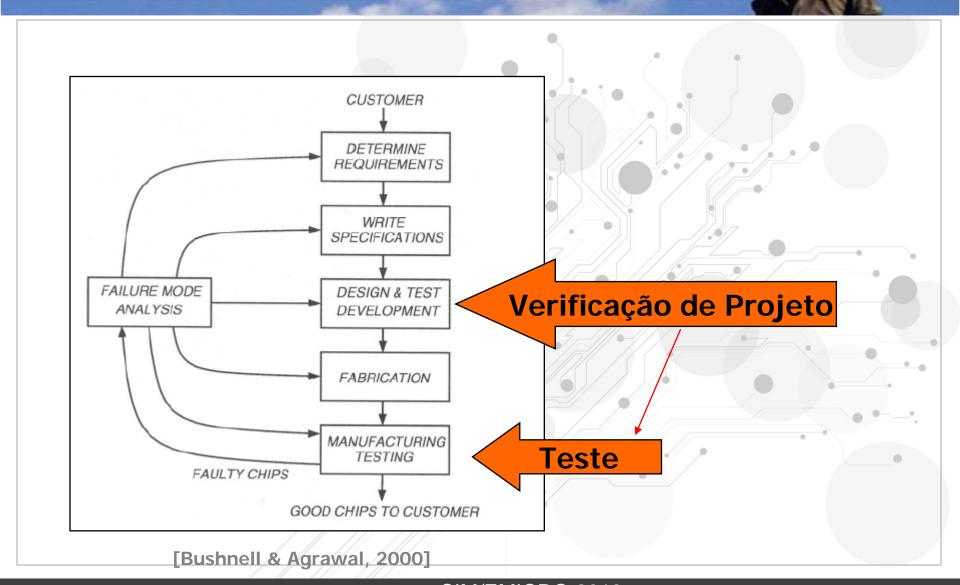

# O Papel do Teste

#### O Papel do Teste

- Quanto à etapa do processo de realização de um CI

- (Teste de verificação)

- Teste de caracterização

- Teste de produção/manufatura

- Burn-in

- Teste de aceitação

Wafer sort

Pós-encapsulamento

- Em geral os Cls são submetidos a dois tipos de teste

- Teste Paramétrico

- DC: curtos, abertos, leakage, capacidade de corrente, níveis de threshold...

- AC: atrasos de propagação, tempos de setup e hold tempos de subida e descida...

- Teste funcional

- Aplicação de vetores de leste e observação das respostas

- Testam o circuito segundo im modelo de falhas

- o Em geral os Cls são submetidos a dois tipos de teste

- Teste Paramétrico

- DC: curtos, abertos, *leakage*, capacidade de corrente, niveis de *threshold*...

- AC: atrasos de propagação tempos de setup e hold tempos de subida e descida...

- Teste funcional

- Aplicação de vetores de teste e observação das respostas

- Testam o se circuito se comporta como esperado

- No entanto um teste funcional completo pode demandar um número muito alto de vetores

- A utilização de modelos de falhas permitem a aplicação do chamado Teste Estrutural e limitam o escopo do teste

- Permite "observar" o estado de sinais internos do circuito através de suas saídas primárias (resposta a vetores específicos)

- Permite o desenvolvimento de algoritmos

#### Modelos de Falhas

- Diferem quanto ao nível de abstração

- Nível comportamental

- Importantes na etapa de verificação (por simulação)

- Nível de registradores (RTL)

- Stuck at 0/1

- Bridging faults

- Delay faults

- Nível de componente

- Stuck on/open (transistores)

- Variações paramétricas em componentes

Mais utilizadas no teste analógico

#### o Exaustiva

- Todas 2<sup>n</sup> combinações são geradas

- Tempo de teste longo

- · Cobertura de falhas alta

1198920341200668243218947683887,8

#### o Exaustiva

- Todas 2<sup>n</sup> combinações são geradas

- Tempo de teste longo

- · Cobertura de falhas alta

1198920341200668243218947683887,8

anos para gerar exaustivamente todos os vetores de teste para um somador de 64 BITs!!!!!!

- o Exaustiva

- Todas 2<sup>n</sup> combinações são geradas

- Tempo de teste longo

- · Cobertura de falhas alta

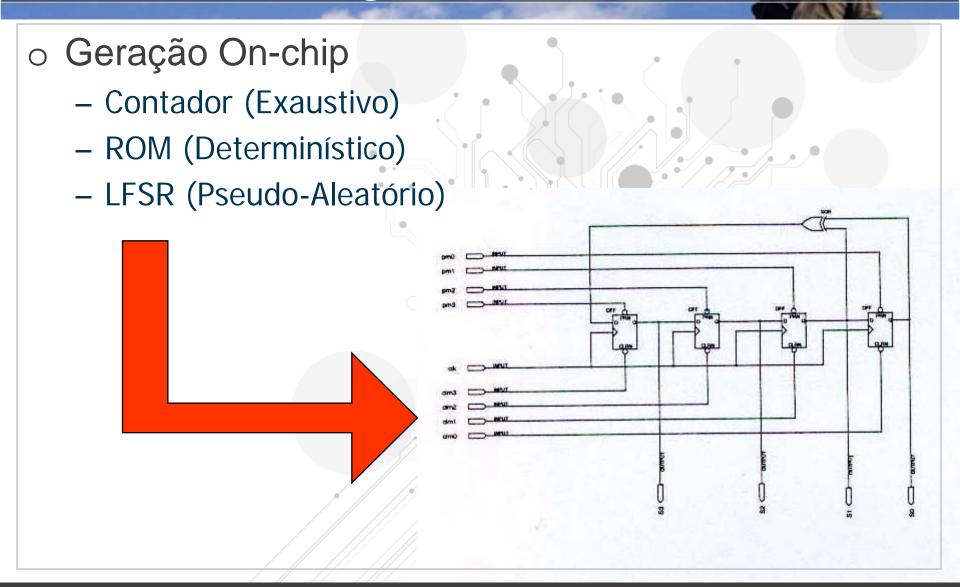

- o Determinística

- Vetores pré-calculados segundo o modelo

- Tempo de aplicação curto

- Alto custo de geração

- o Exaustiva

- Todas 2<sup>n</sup> combinações são geradas

- Tempo de teste longo

- · Cobertura de falhas alta

- o Determinística

- Vetores pré-calculados segundo o modelo

- Tempo de aplicação curto

- Alto custo de geração

- o Pseudo-Aleatória

- Geração aleatória de estímulos

- Tempo de aplicação intermediária

- Associada a algoritmos de ATPG para obter boa cobertura de falhas

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste.

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando à Testabilidade e Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

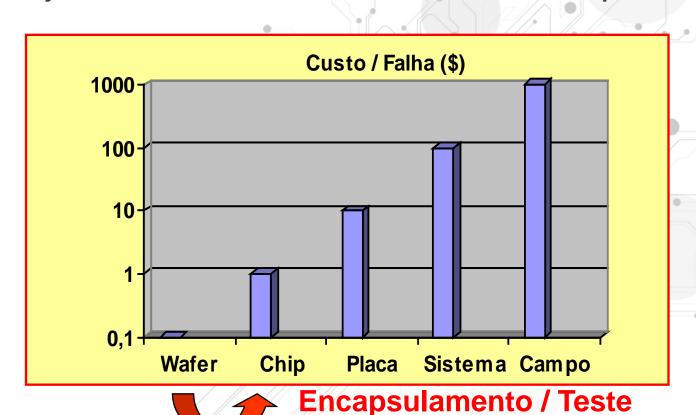

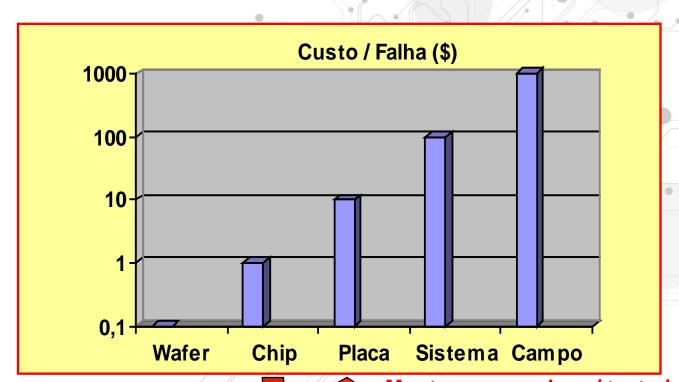

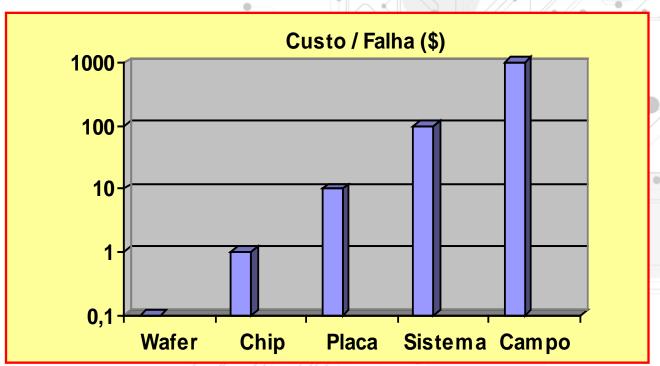

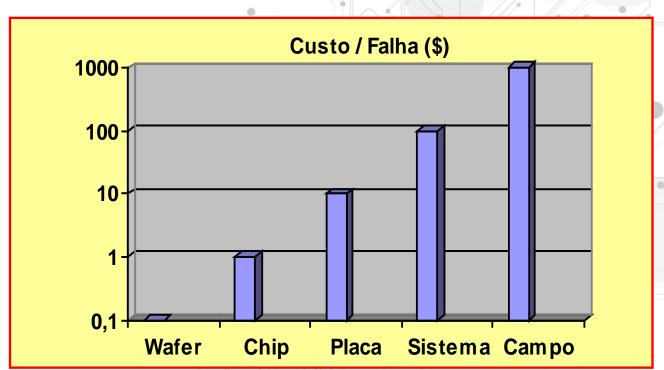

- o Rulle of ten

- Desejável detectar falhas o mais cedo possível

- o Rulle of ten

- Desejável detectar falhas o mais cedo possível

Montagem em placa / teste / diagnóstico / substituição de componentes

- o Rulle of ten

- Desejável detectar falhas o mais cedo possível

- o Rulle of ten

- Desejável detectar falhas o mais cedo possível

Diagnóstico / reparo / garantia / retorno

- Detectar falhas o mais cedo possível

- Teste em produção

- Wafer sort

- Pós-encapsulamento

T6683

**ATEs: Automatic Test Equipments**

\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$\$

Tempo de teste é essencial:

Redução no tempo de teste reduz custo de teste sobre o circuito final

Custo do Teste pode chegar a 50% do custo final de um CI

**Multi Site Testing**

**Example 1.2** Testing cost. A state of the art ATE in the year 2000 applies test vectors at <u>clock rates up to 500 MHz</u>. It contains analog instruments (function generators, A/D converters and waveform analyzers.) The price of this tester for a 1,024 pin configuration is estimated as

$$ATE\ purchase\ price = \$1.2M + 1,024 \times \$3,000 = \$4.272M$$

We compute the yearly running cost of the ATE by assuming a linear depreciation over five years, and an annual maintenance cost of 2% of the purchase price. The operating cost of the building, facilities, auxiliary equipment (wafer and chip handlers, fixtures, etc.), and personnel is estimated to be \$0.5M. Thus:

Running cost = Depreciation + Maintenance + Operating cost

=

$$\$0.854M + \$0.085M + \$0.5M = \$1.439M/year$$

The tester is used in three eight-hour shifts per day and on all days of the year. Therefore:

Testing

$$cost = \frac{\$1.439M}{365 \times 24 \times 3,600} = 4.5 \text{ cents/second}$$

The test time for a digital ASIC (application specific integrated circuit) is 6 seconds. That gives the test cost as 27 cents. Since the bad chips are not sold, their test cost must be recovered from the sale of good chips. If the yield is 65%, then the test component in the sale price of a good chip is 27/0.65 = 41.5 cents.

Custos Variáveis

**Custos Teste**

**Custos Fixos**

**Yield**

[Bushnell & Agrawal, 2000]

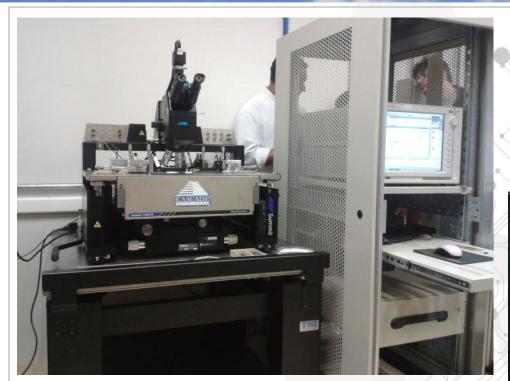

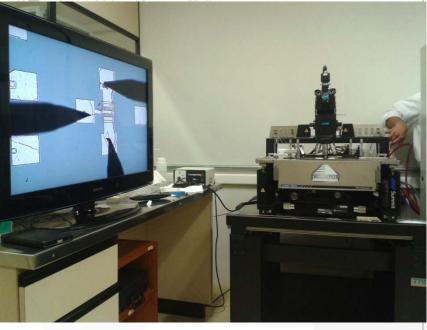

# Exemplo - fotos de testador

# Exemplo - fotos de testador

#### Exemplo - fotos de testador

#### Probe Station + Extrator de Parâmetros

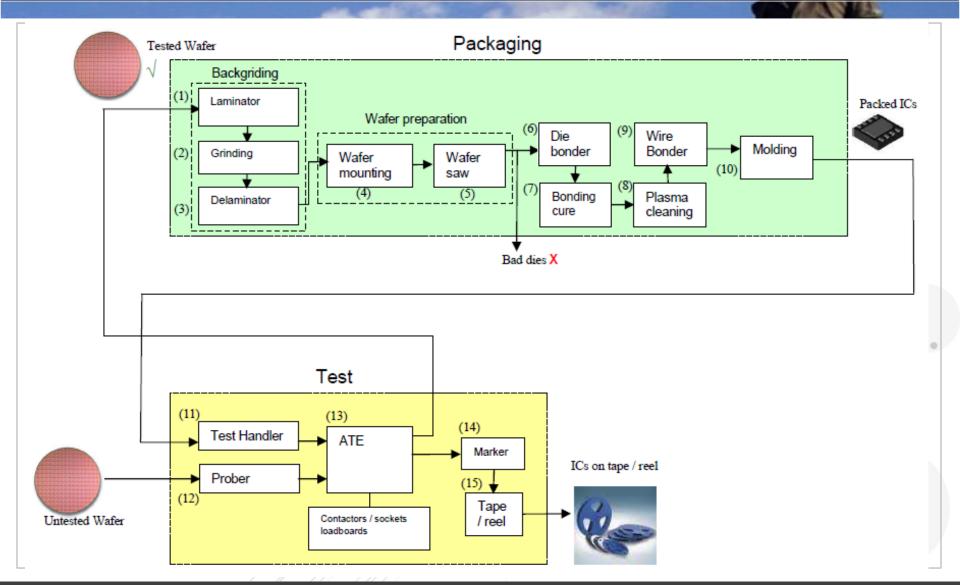

#### Teste de Produção (Exemplo de linha de encapsulamento e teste)

#### Teste de Produção (Exemplo de linha de encapsulamento e teste)

## Modelos de negócios

- Verticalizado Mesma empresa realiza:

- Projeto

- Fabricação

- Teste

- Encapsulamento

- Empresas especializadas em uma ou mais etapas

- Design Houses

- Foundry

- Back end

- Teste

- Encapsulamento

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando a Testabilidade e Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

# Projeto Visando a Testabilidade

- DfT: Design-for-Testability

- Adicionar recursos ao circuito (em nível de projeto), que não são necessários à funcionalidade, para auxiliar no teste

- Circuitos self-checking

- Pontos de acesso interno

- Geradores de vetores

- Analisadores de resposta

Códigos detectores e corretores de erro (paridade, Hamming, Berger...)

Controlabilidade Observabilidade

**Autoteste**

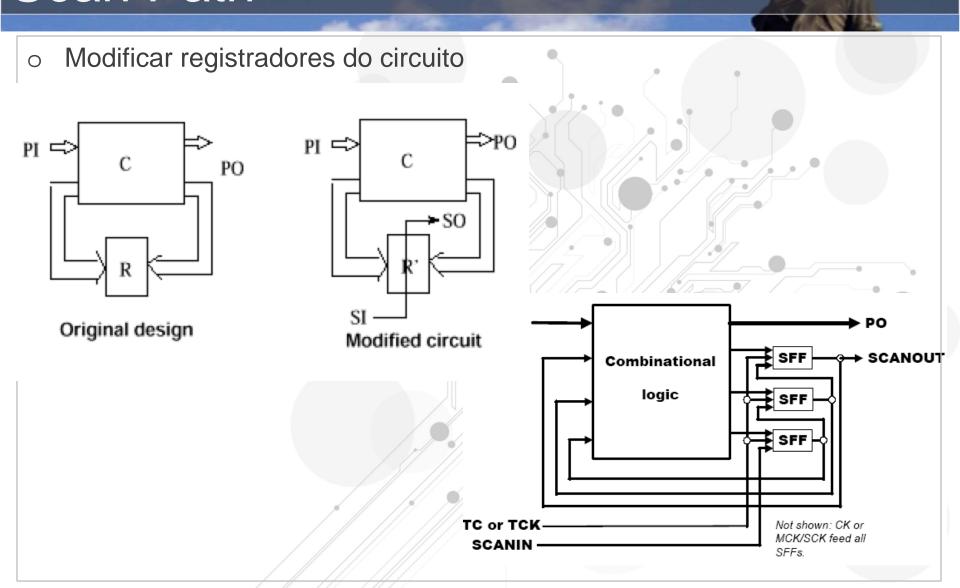

#### Scan Path

- Técnica estruturada muito utilizada em circuitos digitais (automatizada / ferramentas)

- Modificar os registradores do circuito

- Operação normal como elemento de memória

- Em modo teste, operação como registrador de deslocamento transferindo para saída estados internos do circuito

## Scan Path

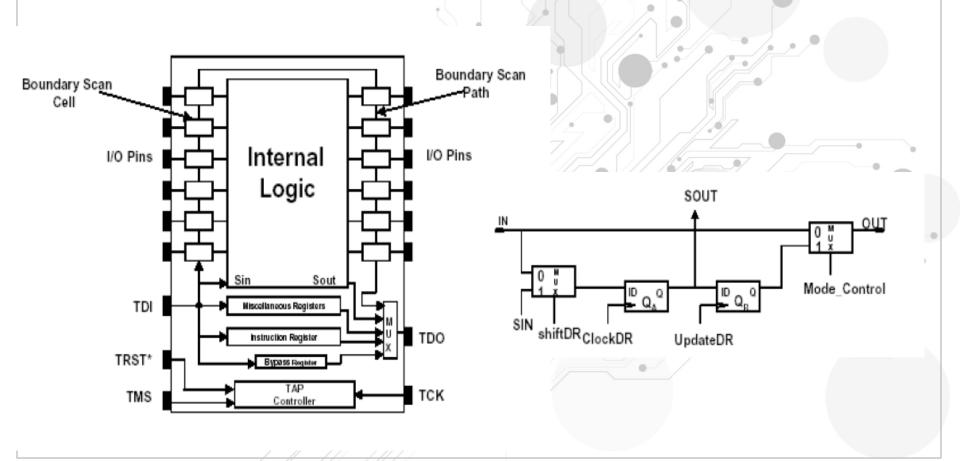

# Padrão IEEE 1149.1 (1990)

Boundary Scan (varredura de periferia)

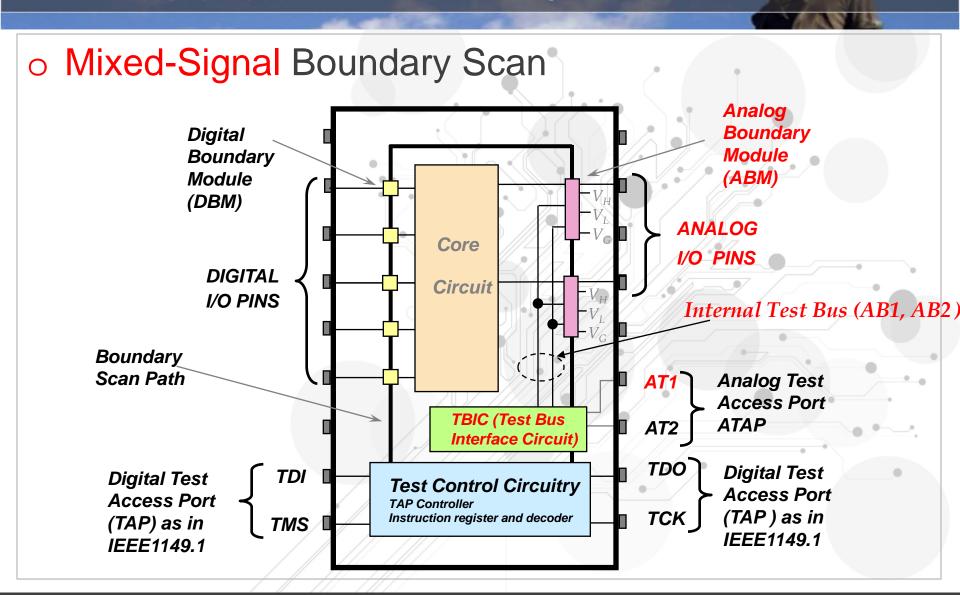

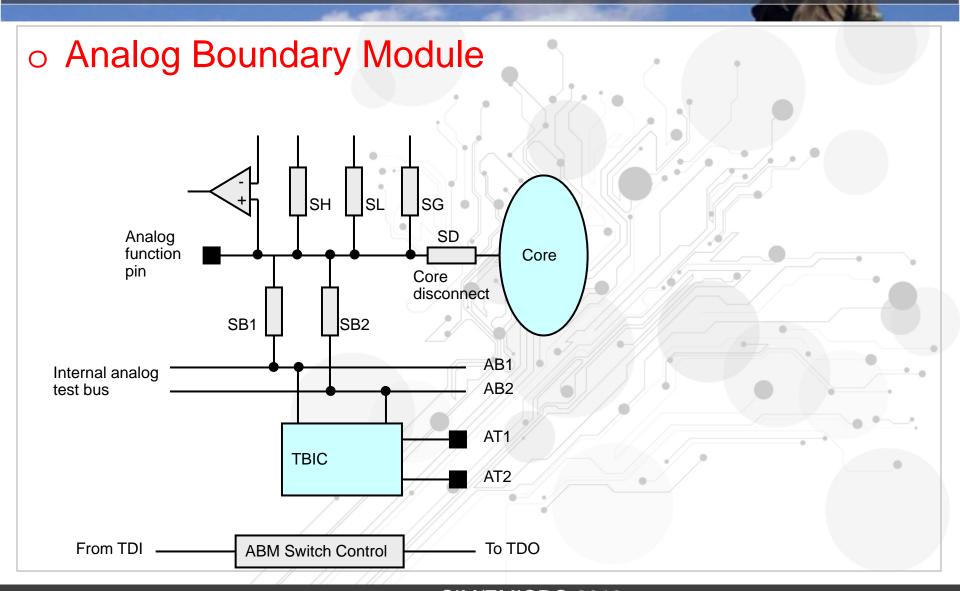

#### DfT: Padrão IEEE 1149.4

#### DfT: Padrão IEEE 1149.4

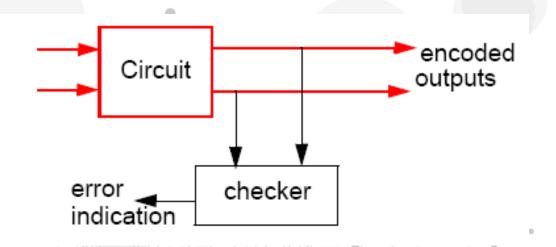

# Circuitos Self-Checking

o Teste On-line

o Tolerância a falhas

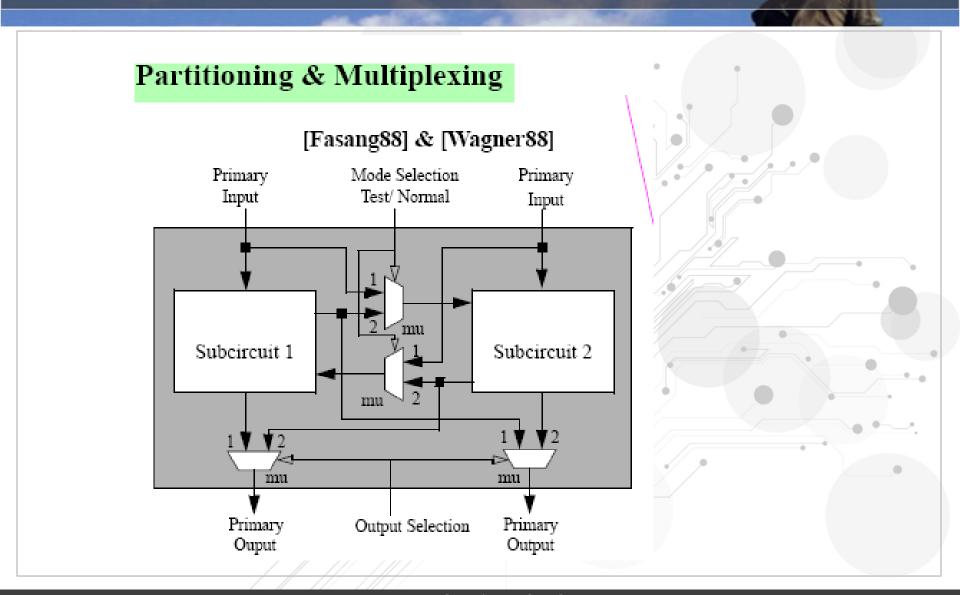

#### Particionamento

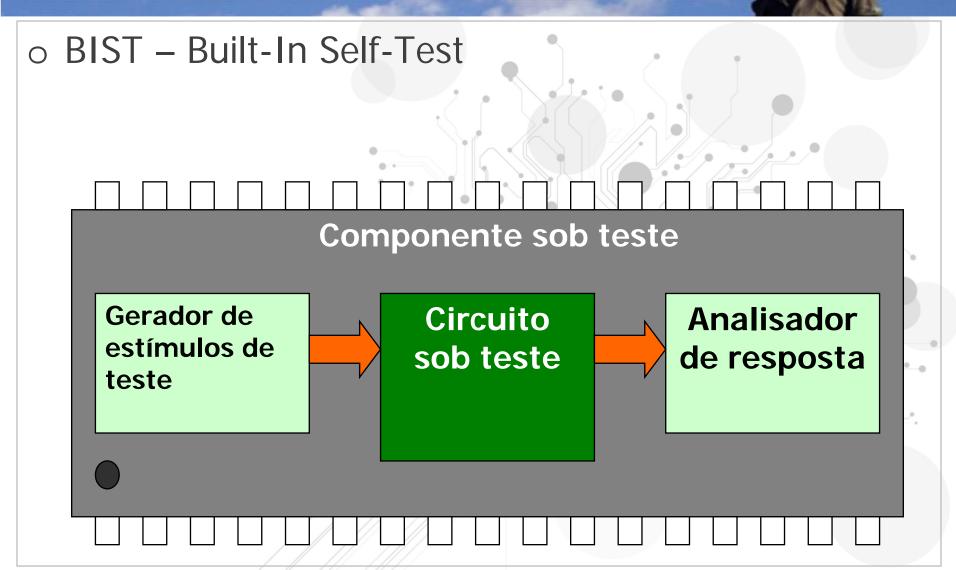

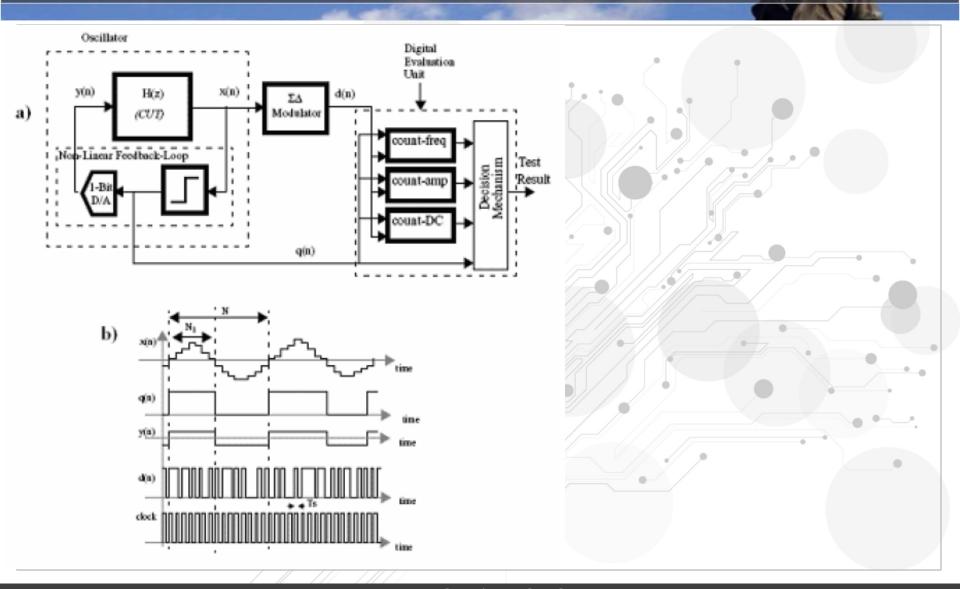

# Auto-teste Integrado

# Auto-teste Integrado

# Auto-Teste Integrado

- Avaliação On-Chip Digital (assinatura do circuito)

- Métodos de compactação

- Contagens de transições 0 para 1

- Contagens do número de 0s

- Divisões polinomiais (LFSR)

- Integração digital (checksum)

# Auto-Teste Integrado

- Avaliação On-Chip Analógico

- Métodos baseados em DSP

- Parâmetros funcionais (THD, SFDR, ENOB..)

- Frequência e amplitude oscilação

- Resposta a estimúlo multi-tom

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando à Testabilidade e

- Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

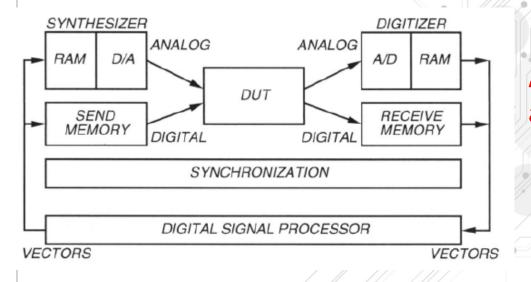

# DfT e Auto-teste Analógico

- Sistemas eletrônicos necessitam de circuitos analógicos para interfaceamento

- o SoCs

- Teste Analógico tão importante quanto teste digital

- Desafios do teste analógico

- Falta de modelo de falhas formal

- Geração de vetores de teste

- Métodos de teste específicos

- Observabilidade em MS-SocS

- Tempo de teste

# Relative Product Cost Evolution | Manufacturing (design, assembly, parts) | Digital Test | Analog Test | | Manufacturing (design, assembly, parts) | Digital Test | Analog Test | | Manufacturing (design, assembly, parts) | Digital Test | Analog Test | | Manufacturing (design, assembly, parts) | Digital Test | Analog Test | | Manufacturing (design, assembly, parts) | Digital Test | Analog Test | | Future

# DfT e Auto-teste Analógico

- Teste baseado em especificações

- THD, SFDR, INL, DNL....

- DSP-based Test (ATEs são caros)

# Alternativas ao teste analógico

Auto-teste integrado Circuitos self-checking

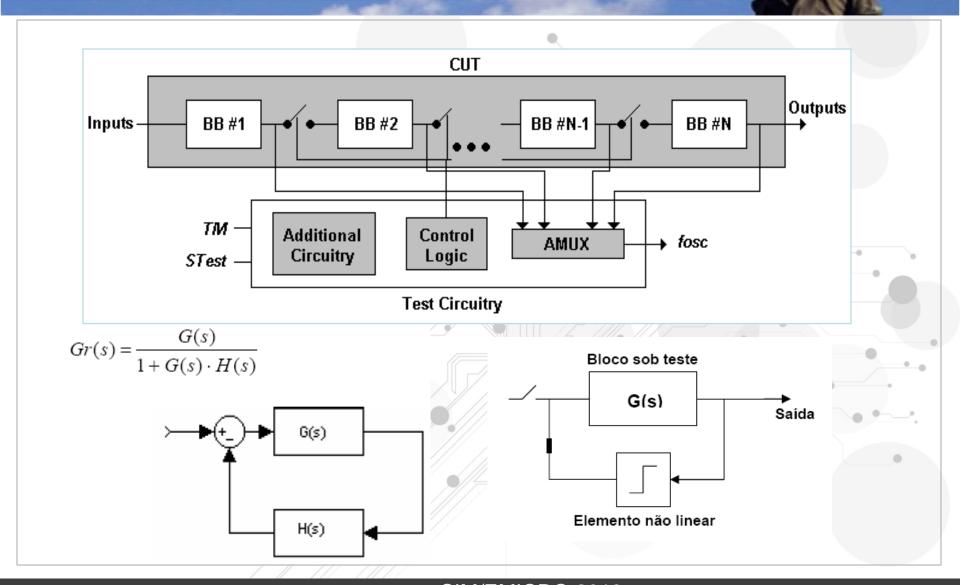

#### Oscillation Based-Test

- Técnica que consiste em particionar um circuito em blocos de segunda ordem e torná-los instáveis

- Não necessita vetores

- Assinatura

- Frequência de oscilação

- Amplitude

- Nível DC

#### Oscillation Based-Test

# **OBT-based BIST**

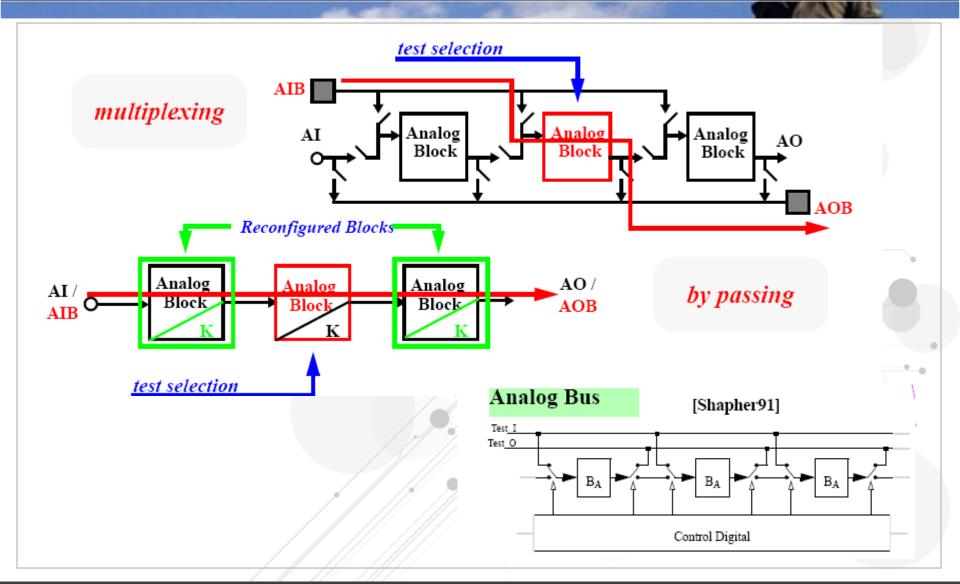

#### Acesso Interno

# Blocos "transparentes"

#### Access implies perturbation:

- observing may limit speed

- controlling requires isolation

- signal path must be preserved

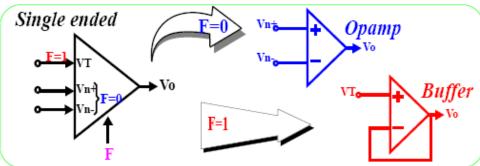

#### The SW-OPAMP: a solution

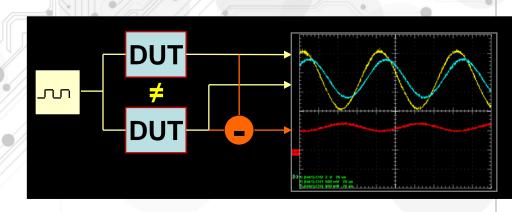

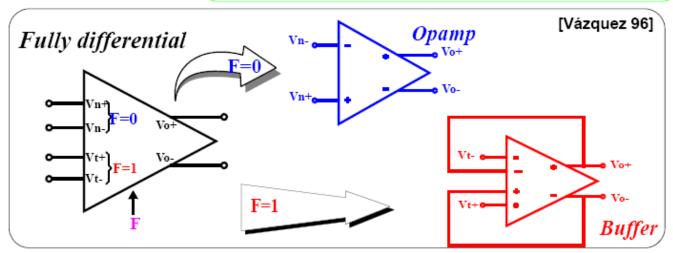

# Replicação Parcial

#### Sumário

- 1) Introdução

- 2) Definições e teoria básica do teste

- 3) Aspectos econômicos e equipamentos

- 4) Projeto Visando a Testabilidade e Autoteste integrado

- 5) DfT e BIST Analógico

- 6) Considerações finais

# Considerações Finais

- Teste tem importante papel na viabilidade econômica do ciclo de concepção de CIs

- Tempo de teste é crucial

- Autoteste integrado e DfT são alternativas

- BIST, Fact or Fiction?

[46] Roberts, G.W.; "Mixed-signal BIST: fact or fiction," Test Conference, 2002. Proceedings. International, vol., no., pp. 1204, 2002

o Just enough test...

## DfT: Desvantagens

- Re-síntese do design

- Hardware extra

- Modificações no circuito afetam:

- área => consumo de energia e yield

- Pinos de I/O

- delay => desempenho

- Tempo de projeto

- Ganhos no teste precisam compensar perdas de desempenho

#### DfT: Vantagens

- Cobertura de falhas

- Tempo de geração (desenvolvimento) de teste

- Tamanho (número de vetores) do teste

- Tempo de aplicação do teste

- Reduz os requisitos do ATE