# Aplicação da metodologia gm/lo para projeto analógico utilizando dispositivos de escala nanométrica

Luiz Antônio da Silva Jr.

Tanísia Possani

Luiz Roberto Pavanato

Alessandro Girardi

Universidade Federal do Pampa Grupo de Arquitetura de Computadores e Microeletrônica

28º Simpósio Sul de Microeletrônica

## Roteiro

- Introdução;

- Objetivos;

- Metodologia;

- Exemplo de projeto;

- Resultados;

- Conclusões.

# Introdução

- Avanço da microeletrônica:

- Aumento da velocidade dos dispositivos;

- Redução do espaço físico utilizado;

- Redução do consumo de potência dos circuitos.

- Estudo de novas tecnologias de transistores:

- FinFET;

- CNTFET.

- Modelos elétricos das novas tecnologias:

- Não fornecem uma relação direta entre corrente, tensão e transcondutâncias.

# **Objetivos**

- Propor uma nova metodologia de projeto analógico adequada a novas tecnologias de fabricação de nanodispositivos;

- Definir uma forma sistemática para projetar circuitos analógicos utilizando:

- Equações do circuito;

- Gráficos auxiliares:

- gm/ld vs ln

- gm/ID vs VGS

- Simulação elétrica.

# Metodologia

- A metodologia de projeto gm/lo considera a relação entre a transcondutância gm sobre a corrente DC lo e a corrente de dreno normalizada IN=ID/(W/L) como a variável fundamental de projeto;

- Está relacionada ao desempenho dos circuitos analógicos;

- Fornece um indicativo da região de operação do dispositivo;

- Proporciona uma estimativa bastante precisa para o cálculos das dimensões dos transistores.

## Metodologia

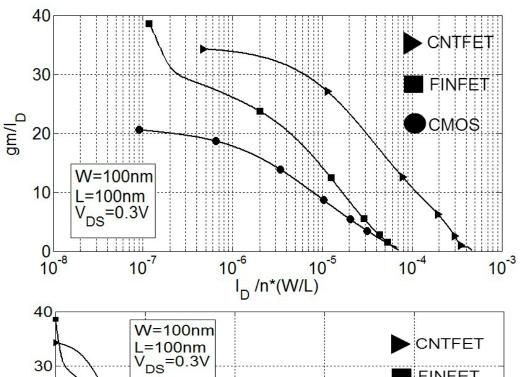

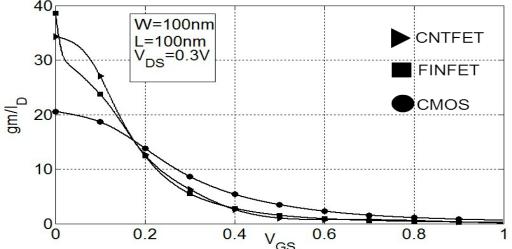

Gráficos simulados para transistor do tipo n

### Relação:

$$\frac{gm}{I_D} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial V_{GS}} = \frac{\partial (\ln(I_D))}{\partial V_{GS}}$$

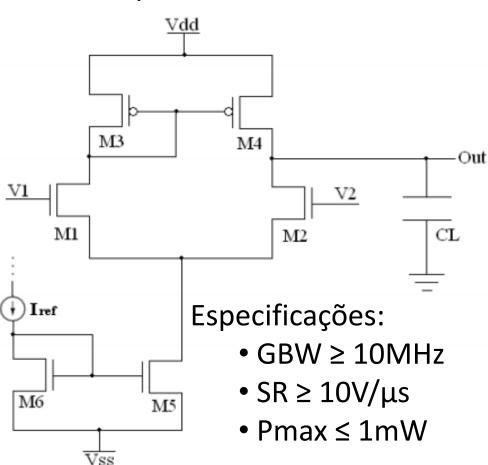

## **Exemplo de Projeto**

#### Amplificador diferencial:

#### Projetar com as tecnologias:

- CMOS 32nm;

- FinFET 32nm;

- CNTFET 32nm.

#### Visando dimensionar:

- A largura de gate p/ CMOS;

- O nº de fins p/ FinFET;

- O nº de nanotubos p/ CNTFET.

Comprimento de gate fixado em 100nm.

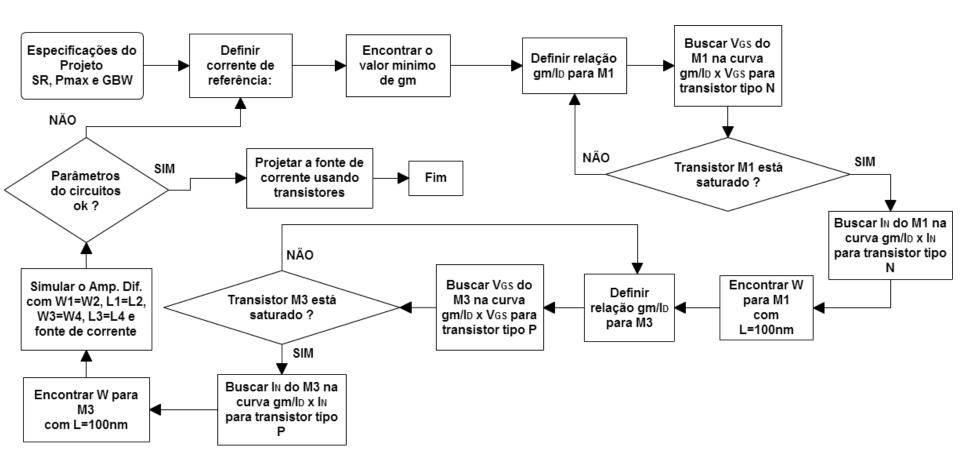

## Exemplo de Projeto

Fluxograma do projeto:

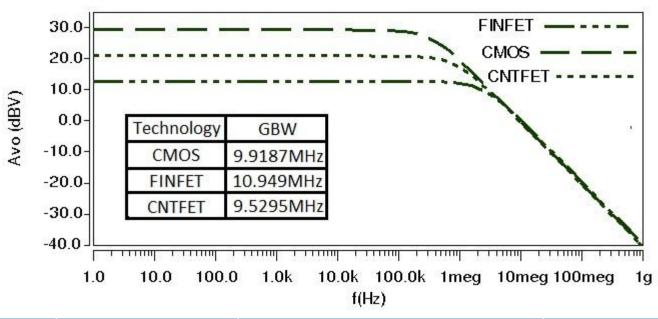

## Resultados

| Tecnologia | Transistor | Largura de Gate    | Potência | SR        |

|------------|------------|--------------------|----------|-----------|

| CMOS       | M1, M2     | 1,08μm             | 176,72μW | 10,64V/μs |

|            | M3, M4     | 9,53μm             |          |           |

|            | M5, M6     | 0,56μm             |          |           |

| FINFET     | M1, M2     | W=3*160nm=480nm    | 182,16μW | 15,81V/μs |

|            | M3, M4     | W=7*160nm=1120nm   |          |           |

|            | M5, M6     | W=3*160nm=480nm    |          |           |

| CNTFET     | M1, M2     | W=22*3,01nm=66,3nm | 171,10μW | 9,35V/μs  |

|            | M3, M4     | W=22*3,01nm=66,3nm |          |           |

|            | M5, M6     | W=13*3,01nm=39,2nm |          |           |

## Conclusões

- A metodologia gm/ID mostrou-se apropriada para o projeto de blocos analógicos compostos por dispositivos em escala nanométrica, como CMOS, FinFET e CNTFET;

- A metodologia gm/ID mostrou ser uma alternativa para o projeto com novos dispositivos sem que haja a necessidade de o projetista conhecer com detalhes o modelo elétrico da tecnologia;

- Como trabalhos futuros, pretende-se explorar a metodologia gm/ID incluindo também uma etapa de projeto para o comprimento de canal dos dispositivos.

#### 28º Simpósio Sul de Microeletrônica

## **Obrigado!**

Luiz Antônio da Silva Jr.

luizjunior@alunos.unipampa.edu.br

Portal UNIPAMPA

www.unipampa.edu.br

**GAMA**

http://alegrete.unipampa.edu.br/gama

Apoio:

Fundação de Amparo à Pesquisa do Estado do Rio Grande do Sul

**Universidade Federal do Pampa**Campus Alegrete

Grupo de Arquitetura de Computadores e Microeletrônica UNIPAMPA