# Delay Model for Static CMOS Gates Considering Single Input Multiple Transistor Switching

Felipe Marranghello, André Reis and Renato Ribas Institute of Informatics, UFRGS, Porto Alegre, RS

{fsmarranghello,andreis,rpribas}@inf.ufrgs.br

#### **Motivation**

- The standard cell methodology is widely used

- Finite set of cells

- Impact circuit performance

- Electrical behavior of the cells must be known

- Electrical simulations

- Library free methodology

- Cells can be generated on-the-fly

- How to know the electrical behavior?

- Electrical simulations become prohibitive

- Analytical models are alternatives

## Analytical delay models

- Deriving analytical delay model is a hard task

- Non-linear circuits

- Several second-order efffects:

- Channel length modulation, drain induced barrier lowering, body effect...

- Multiple possible switching scenarios

## Analytical delay models

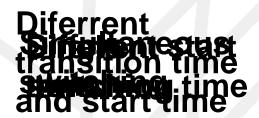

- Timing analysis can consider that only one input switches

- Most models assume that only one NMOS and one PMOS switch

- Valid assumption for common gates in libraries

## Work proposal

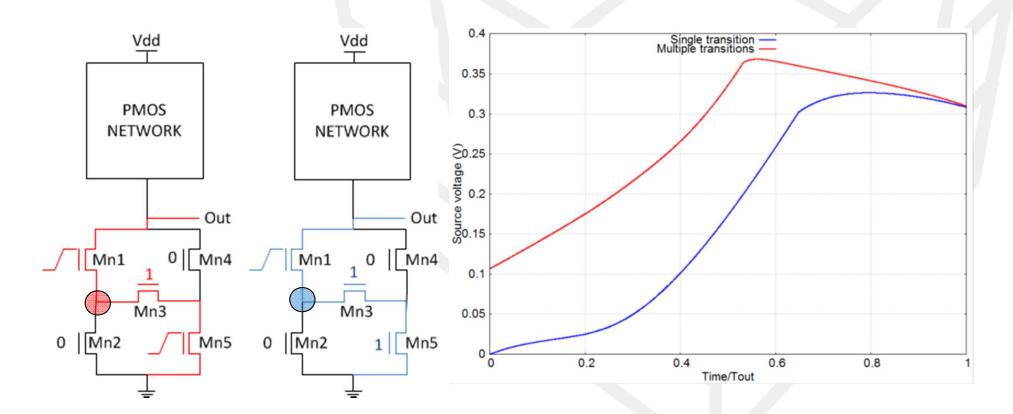

- In some cases, the impact of simultaneous switching is important

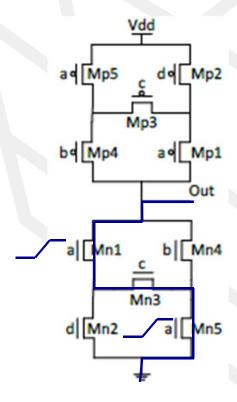

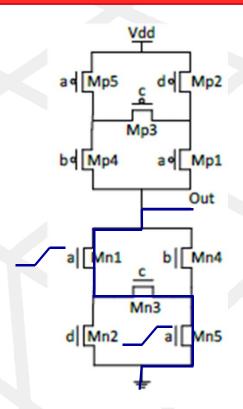

- This work proposes an analytical delay model to consider two stacked transistor switching simultaneously

- Extension to previous work

## Deriving an analytical delay model

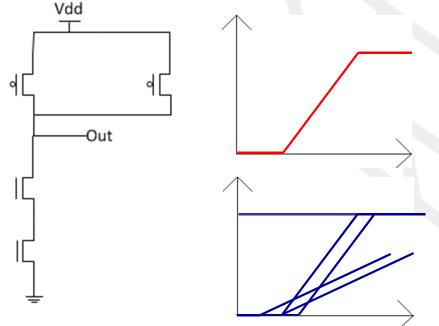

- Analytical delay models estimate

- Required charge to cause the output voltage drop

- Discharge current

## Deriving an analytical delay model

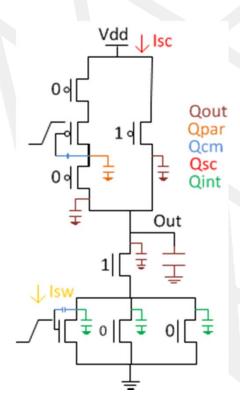

- Required charge to cause the output voltage drop

- Internal capacitances, output load, short circuit current, I/O coupling capacitance

## Deriving an analytical delay model

- Discharge current

- Switching transistor applied voltages

- Discharge current estimation is different for simultaneous switching

#### Results

- Industrial 65 nm technology

- ♦ Average error ≈3%

- Worst case <10%</p>

| Load | AVG (%) | WC (%) |

|------|---------|--------|

| 0.25 | 2.56    | 8.70   |

| 1    | 2.52    | 8.24   |

| 4    | 3.34    | 7.61   |

| 16   | 4.23    | 7.50   |

| 64   | 3.04    | 7.59   |

| 256  | 1.85    | 2.46   |

Similar to reported errors of models focusing on single transition

| Work            | AVG (%) | WC (%) |

|-----------------|---------|--------|

| Wang [16]       | < 5     | NA     |

| Kabbani [15]    | 4.5     | 7.5    |

| Lasboygues [14] | 3       | 9      |

| Rossello [13]   | 3       | NA     |

| Daga [12]       | NA      | <10    |

## Thank you!

Institute of Informatics, UFRGS, Porto Alegre, RS

{emails}@inf.ufrgs.br