# A Resistorless Switched Bandgap Reference Topology

Hamilton Klimach\*, Moacir Fernandes Cortinhas Monteiro<sup>†</sup>, Arthur Liraneto Torres Costa<sup>†</sup> and Sergio Bampi<sup>†</sup>

\*PGMicro - Departamento de Engenharia Eletrica

Universidade Federal do Rio Grande do Sul, Porto Alegre-RS 90035-190

Email: hamilton.klimach@ufrgs.br †PGMicro - Instituto de Informatica

Universidade Federal do Rio Grande do Sul, Porto Alegre-RS 91501-970

Email: mfcmonteiro@inf.ufrgs.br Email: altcosta@inf.ufrgs.br Email: bampi@inf.ufrgs.br

Abstract—This work presents a novel Switched-capacitor Bandgap Reference circuit using no resistors at all. The negative drift  $V_{EB}$  and the positive drift  $V_T$  voltages are generated by the same PNP bipolar transistor. A switched-capacitor circuit stores and processes these voltages, generating the bandgap reference voltage in only 4 clock phases. The proposed topology was simulated in CMOS 130nm process, presenting better performance than tradicional band-gap topologies. Monte Carlo simulation shows lower variability, that results from the lower variability of capacitor ratios instead of resistor ratios and from the use of just one bipolar transistor.

# I. INTRODUCTION

Voltage references, besides operational amplifiers, are fundamental blocks that are present today in every analog, mixed-signal, and even digital design. They are essencial for bias, data-conversion, power regulation and management, and almost any other electronic circuit implementation. Its most important characteristic is to offer a voltage that is very insensitive to temperature variations, presenting a good thermal stability. Also, this voltage must be almost the same in any fabricated unit, which means that the circuit topology has to be very insensitive to uncontrollable factors in process fabrication that cause device mismatch.

Bandgap voltage reference is one of the most relevant circuits that successfully achieve these requirements, but as CMOS technology continues to shrink its size, resulting in larger variation in device parameters, it becomes more and more difficult to design precise bandgap references. As a consequence, traditional topologies such as in [1] are becoming unable to handle this challenge.

A lot of work has been done in order to improve bandgap reference's performance, such as in [2] based on weighted  $\Delta V_{GS}$ , using curvature compensation of higher order temperature terms [3], [4], using only one BJT and MOSFETs in weak inversion [5] and using resistor trimmers to adjust process and mismatch errors [6]. Most of them use the same technique proposed originally by Robert Widlar in 1971's LM113 [7], the first commercial bandgap reference, where the difference of the  $V_{BE}$  voltages of two bipolar transistors, working under

different junction current densities, is applied over a resistor to generate a proportional-to-absolute-temperature (PTAT) current. Then, this current is applied to another resistor which value is calculated to make its voltage drop counterbalance the almost linear negative voltage drift of a bipolar junction under forward bias, around -2mV/°C.

The work in [8] describes the process and mismatch variation dependency of bandgap references and proposes a process-mismatch design-oriented strategy. It presents the dependency of the bandgap voltage on resistors and current mirrors mismatch. Furthermore, [9] proposes a bandgap reference with intrinsic compensation, in order to solve the current mirror mismatch problem and [10] proposes a bandgap reference without resistors. However, [9] depends on resistors good matching, and [10] on many current mirrors matching.

In this work, we propose a resistorless switched bandgap reference topology, which presents better voltage standard deviation due to device mismatch when comparing with a traditional bandgap reference using resistors. The topology presented uses a single current mirror, a single BJT, along with switched capacitors to implement the bandgap PTAT plus  $V_{EB}$  voltage computing with matching improved. The circuit gain depends on capacitors matching, which is far more accurate than resistors in current CMOS processes. Moreover, lower thermal noise is produced.

For comparison purposes, we present simulations from our topology compared to the traditional one in CMOS 130 nm process. Thermal behavior and Monte Carlo simulations using Cadence Virtuoso are shown.

This paper is organized as follows: section II introduces the concept and characteristics of a switched-capacitor bandgap reference circuit; section III presents the results of nominal voltage variation with temperature, control signals and Monte Carlo simulations, as well as Monte Carlo comparisons; and section IV presents the conclusions.

### II. THE SWITCHED BANDGAP CIRCUIT

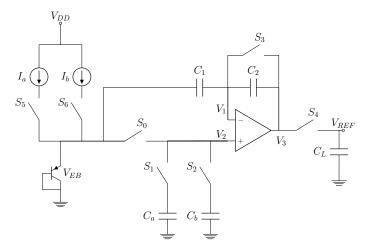

In our topology, the bandgap reference is based on the cancelation of the almost linear negative voltage drift of a bipolar junction, around -2mV/°C, by the proportional-to-absolute-temperature (PTAT) difference of the junction voltages of the same bipolar transistor, working under two different junction current densities. The switched bandgap reference proposed in this work is shown in Fig. 1. The op-amp is initially considered ideal for a simpler explanation.

The equation for the  $V_{EB}$  voltage as a function of its current I is approximately given by

$$V_{EB} = V_T \cdot ln \frac{I}{I_S} \tag{1}$$

being  $V_T$  the thermal potential and  $I_S$  the junction reverse saturation current. Subtracting two  $V_{EB}$  voltages generated by different currents, i.e., I and 2I, the following equation holds

$$V_{EB_1} - V_{EB_2} = V_T \cdot ln \frac{2I}{I_S} - V_T \cdot ln \frac{I}{I_S}$$

(2)

$$\Delta V_{EB} = V_T \cdot ln2 = \frac{kT}{q} \cdot ln2 \tag{3}$$

where k is the boltzman constant, T the temperature and q the electron charge. One can see in (3) that the voltage  $\Delta V_{EB}$  is proportional to temperature. Also, the junction voltage  $V_{EB}$  shows a negative temperature drift, which to first order can be approximated by

$$V_{EB} = V_{EB}(T_0) - \alpha(T - T_0)$$

(4)

where  $\alpha$  is around 2mV/°C. If one sums eqs. (3) and (4) with the correct gain in the first one, the bandgap reference is then obtained.

The switched bandgap reference proposed here does exactly as described above using switched capacitors, as shown in Fig 1. A single capacitor could be used instead of two ( $C_a$  and  $C_b$ ), however the circuit would be more susceptible to current mismatches from the mirror ( $I_a$  and  $I_b$  should be equal). Let's suppose that  $I_a$  and  $I_b$  are almost equal, and its difference results from MOSFETs mismatch.

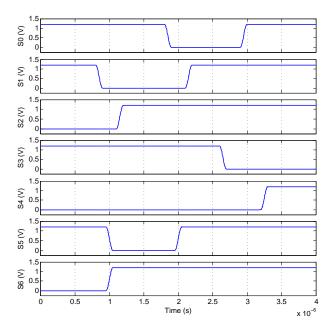

The behavior of this circuit is divided into 4 phases (assume the switches that are not closed are openned) for switches control:

- Phase 1) Switches S0, S1, S3 and S5 are closed and the capacitor  $C_a$  is charged to  $V_{EB}(I_a)$ ;

- Phase 2) Switches S0, S2, S3 and S6 are closed and the capacitor C<sub>b</sub> is charged to V<sub>EB</sub>(I<sub>b</sub>);

- Phase 3) Switches S1, S2, S3, S5 and S6 are closed causing:

- Average of  $V_{Ca}$  and  $V_{Cb}$  to  $V_{EB}(I_{ab})$ ;

- The capacitor  $C_1$  is charged to the difference between  $V_{EB}(I_a + I_b)$  and  $V_{EB}(I_{ab})$ ;

- Phase 4) Switches S0, S1, S2, S4, S5 and S6 are closed and the output  $V_{REF}$  goes to its final value;

In phase 3, charges in  $C_a$  and  $C_b$  are averaged, making the voltage  $V_{EB}(I_{ab})$  an intermediate result from currents  $I_a$  and  $I_b$ . Since both currents are summed in this phase to generate

$V_{EB}(I_a+I_b)$ , this average reduces the impact of the mismatch between the mirror currents, resulting

$$\Delta V_{EB} = V_{EB}(I_a + I_b) - V_{EB}(I_{ab}) \approx \frac{kT}{q} \cdot ln2$$

(5)

In this phase the charge stored in  $C_1$  is given by

$$\Delta Q_1 = \Delta V_{EB} \cdot C_1 \tag{6}$$

as in phase 4 the charge in  $C_1$  is transferred to  $C_2$ , it yields

$$V_{C2} = \frac{\Delta V_{EB} \cdot C_1}{C_2} \tag{7}$$

Finally, the output voltage of the circuit is given by

$$V_{REF} = V_{C2} + V_{EB} \tag{8}$$

$$V_{REF} = \frac{C_1 k}{C_2 q} \cdot ln2 \cdot T + V_{EB}(T_0) - \alpha(T - T_0)$$

(9)

The thermal dependency is canceled if

$$\frac{C_1}{C_2} = \frac{\alpha \cdot q}{k \cdot ln2} \tag{10}$$

which is the amplifier gain. One can easily adjust the amplifier gain by simulations, using typical parameters and canceling thermal dependency for 300K. In our case, we obtained the optimum value of 25.6.

Fig. 1. Switched bandgap reference circuit.

### III. SIMULATION RESULTS

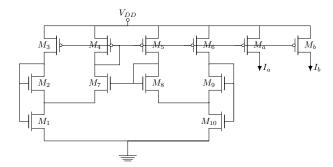

The switched bandgap reference circuit was simulated with Cadence Virtuoso Spectre, using IBM 130 nm technology PDK. Electrical simulations used the foundry-supplied parameters for MOSFET model BSIM4. The ideal current sources were replaced by a mirror, controlled by the current bias source proposed in [11], which is also shown in Fig. 2. This current source uses no resistors and can be designed to have a good matching and acceptable temperature variation. For

this simulation we designed the mirror for 10uA, but lower currents could be used.

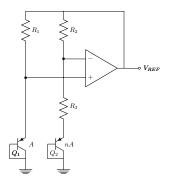

The traditional bandgap topology was designed to work with the same currents in the bipolar transistors. Since the process used offers many options for resistors, it was designed using OPRP (precision poly resistor), which would result in a large area taken for their layout. This circuit is shown in Fig. 3, being the base of most bandgap references. The start-up circuit is not shown. In this simulation we used R1 = R2 to keep the same current in both arms, and n = 2, meaning Q2 works with half the current density of Q1.

Both circuits were designed to operate in similar conditions, and the operational amplifier was modeled as ideal in both circuis, to focus on the circuit topology comparison.

Fig. 2. Current bias source used for simulations.

Fig. 3. Traditional bandgap reference circuit.

The  $V_{REF}$  equation for this traditional circuit is:

$$V_{REF} = V_{EB_1} + V_T \cdot ln(n) \frac{R_2}{R_3}$$

(11)

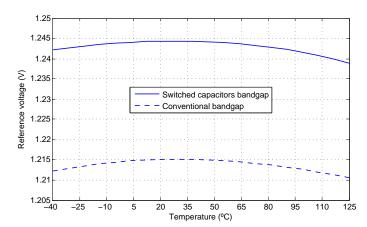

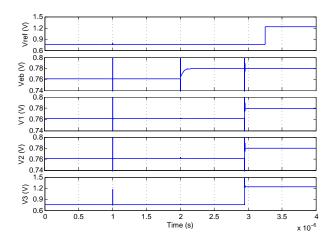

Fig. 4 shows  $V_{REF}$  vs temperature simulation results from both circuits, using typical parameters. The switched bandgap voltage has a 5 mV variation around 1.24 V, while the traditional bandgap voltage has the same variation around 1.21 V. From the temperature drift point of view, both circuits behave similarly.

The time behavior of voltages  $V_1$ ,  $V_2$  and  $V_3$  of Fig. 1 are shown in Fig. 5. The control signals of switches S0 to S6 are shown in Fig. 6. They follow the description of the 4 phases in the previous section.

Fig. 4.  $V_{REF}$  vs Temperature curves.

Fig. 5. Intermediate voltage signals.

Fig. 6. Control signals for the switches.

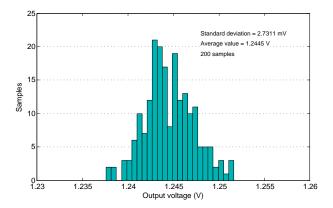

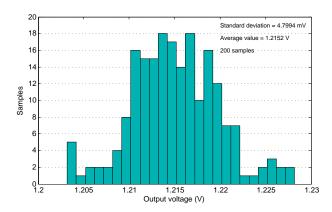

Monte Carlo simulation of device mismatch impact in

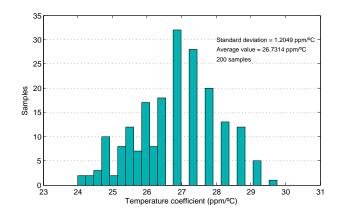

$V_{REF}$ , for 200 samples and 27 °C , is presented in Fig. 7 and Fig. 8, showing that the switched bandgap circuit presents a standard deviation in  $V_{REF}$  of 2.7 mV against the 4.8 mV presented by the traditional topology. This improvement results mainly from the use of capacitors instead of resistors in this topology. The use of only one bipolar transistor, and the mirror mismatch effect reduction by charge averaging, also contributed for the better performance. In simpler and lower cost processes, where precision resistors are not an option, this performance difference would increase. Also, the area taken by the critical capacitors ( $C_1$  and  $C_2$ ) is lower than the area used by the resistors. In Fig. 9 one can see the Temperature Coefficient (TC) variation of the switched bandgap presenting a mean value of 26.7 ppm/°C and a maximum of 30.3 ppm/°C for  $3\sigma$ .

Fig. 7. Monte Carlo simulation for the switched bandgap.

Fig. 8. Monte Carlo simulation for the traditional bandgap.

## IV. CONCLUSION

We have introduced a new resistorless bandgap reference topology concept, without resistors, which offers lower variability based on better matching properties of capacitors in commercial processes. Also, bipolar current density variability, related to current mirror mismatch, is compensated by charge averaging in different phases. In simulations using IBM 130nm PDK, the reference voltage of the proposed circuit presented half the standard deviation of a traditional topology, working

Fig. 9. Monte Carlo thermal drift simulation for the switched bandgap.

under similar conditions and using precision resistors. Also, a average TC of 26.7 ppm/°C enables this circuit to be used without calibration in many applications.

#### ACKNOWLEDGMENT

The authors would like to thank PRONEX/CNPq and Capes for the funding support given to this research.

#### REFERENCES

- [1] K. Kuijk, "A precision reference voltage source," *Solid-State Circuits*, *IEEE Journal of*, vol. 8, no. 3, pp. 222 –226, june 1973.

- [2] K. N. Leung and P. Mok, "A cmos voltage reference based on weighted delta;vgs for cmos low-dropout linear regulators," *Solid-State Circuits*, *IEEE Journal of*, vol. 38, no. 1, pp. 146 – 150, jan 2003.

- [3] K. N. Leung, P. Mok, and C. Y. Leung, "A 2-v 23- μa 5.3-ppm/ deg;c 4th-order curvature-compensated cmos bandgap reference," in Custom Integrated Circuits Conference, 2002. Proceedings of the IEEE 2002, 2002, pp. 457 – 460.

- [4] C. Y. Leung, K. N. Leung, and P. Mok, "Design of a 1.5-v high-order curvature-compensated cmos bandgap reference," in *Circuits and Systems*, 2004. ISCAS '04. Proceedings of the 2004 International Symposium on, vol. 1, may 2004, pp. I 48–52 Vol.1.

- [5] A. Lahiri and N. Agarwal, "Design of sub-1-v cmos bandgap reference circuit using only one bjt," *Analog Integrated Circuits and Signal Processing*, vol. 71, pp. 359–369, 2012.

[6] R. Paul and A. Patra, "Trimming process and temperature variation

- [6] R. Paul and A. Patra, "Trimming process and temperature variation in second-order bandgap voltage reference circuits," *Microelectronics Journal*, vol. 42, no. 2, pp. 271 – 276, 2011.

- [7] R. Widlar, "New developments in ic voltage regulators," *Solid-State Circuits, IEEE Journal of*, vol. 6, no. 1, pp. 2 7, feb 1971.

- [8] V. Gupta and G. Rincon-Mora, "Predicting and designing for the impact of process variations and mismatch on the trim range and yield of bandgap references," in *Quality of Electronic Design*, 2005. ISQED 2005. Sixth International Symposium on, march 2005, pp. 503 – 508.

- [9] S. Li, X. Zou, X. Chen, Z. Zou, K. Yu, and H. Zhang, "A precise bandgap reference with intrinsic compensation for current-mirror mismatch," in *Circuits and Systems*, 2008. APCCAS 2008. IEEE Asia Pacific Conference on, 30 2008-dec. 3 2008, pp. 1200 –1203.

- [10] A. Buck, C. McDonald, S. Lewis, and T. Viswanathan, "A cmos bandgap reference without resistors," *Solid-State Circuits, IEEE Journal* of, vol. 37, no. 1, pp. 81 –83, jan 2002.

- [11] E. Camacho-Galeano, C. Galup-Montoro, and M. Schneider, "A 2-nw 1.1-v self-biased current reference in cmos technology," *Circuits and Systems II: Express Briefs, IEEE Transactions on*, vol. 52, no. 2, pp. 61 – 65, feb. 2005.