Geração de layout

a partir da descriçãoVHDL

de um circuito digital utilizado

as bibliotecas AMS

1 Introdução a Ferramenta Mentor

Graphics

2 Síntese de Circuitos

Integrados

3 Ferramenta: Design Manager

(dmgr)

4 Ferramenta: Design

Architecture (da)

5 Ferramenta: Simulador QuickSim

6 Ferramenta: Autologic II

(alui)

7 Ferramenta: Design

View Point (DVE)

8 Ferramenta: IC Station (ic)

O sistema Mentor Graphics é composto por diversas ferramentas responsáveis pela síntese, validação e teste de circuitos integrados. Essas ferramentas são: compilador de descrições de alto nível de circuitos digitas, simuladores lógicos e elétricos, mapeador tecnológico, posicionador, roteador, extrator elétrico, compactador de layout e outras.

Cada ferramenta pode ser chamada em separado digitando diretamente sua chamada no command tool, ou pode ser chamada de dentro da janela da ferramenta principal da Mentor chamada Design Manager.

O objetivo deste tutorial é mostrar passo a passo a síntese de um circuito digital no sistema Mentor. Este tutorial parte da descrição VHDL de um circuito e mostra como fazer a síntese do layout Standard cell a partir desta descrição utilizando as células da biblioteca da AMS.

O layout chamado de Standard cell (mar de células) é composto de células lógicas, projetadas e testadas anteriormente e descritas em uma biblioteca de células, posicionadas em bandas separadas por canais de roteamento. A biblioteca da AMS é concedida pela fábrica e conectada ao sistema Mentor a fim de sintetizar circuitos para a fabricação na AMS (Austria).

1.1 Configuração do ambiente

Para chamar o sistema Mentor, e consequentemente todas as suas ferramentas,

deve-se acrescentar ao .login as seguintes linhas:

source /gme/cadtool/pub/login.mentor

source /gme/cadtool/pub/login.kitams

Antes de chamar o Design Manager da janela command tool,

execute o comando:

> source .login

Se ocorrer algum erro após a chamado do Mentor, então

execute os comandos:

> unsetenv LANG

> source .login

2 Síntese de Circuitos Integrados

A figura 2.1 ilustra o fluxo da síntese de circuitos integrados começando na descrição de alto nível e chegando ao layout Standard Cell. Todos esses passos são cobertos pelo sistema Mentor e estão descritos neste tutorial.

Figura 2.1 Fluxograma de projeto

Os passsos de simulação são extremamente importantes para a validação da descrição do circuito e posteriormente para avaliação do funcionamento e desempenho do circuito.

3 Ferramenta: Design Manager (dmgr)

A ferramenta Design Manager é visualizada no ambiente Falcon Framework. Todas as demais ferramentas instaladas no sistema Mentor podem ser chamadas de dentro do Design Manager.

3.1 Chamada da ferramenta

Na linha de comando digitar:

> dmgr

Para o ambiente AMS, digitar:

> ams_dmgr

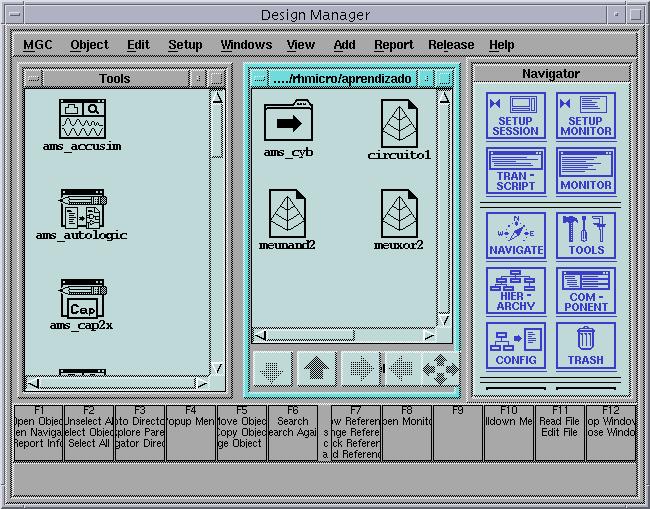

A figura 3.1 mostra a janela da ferramenta Design Manager.

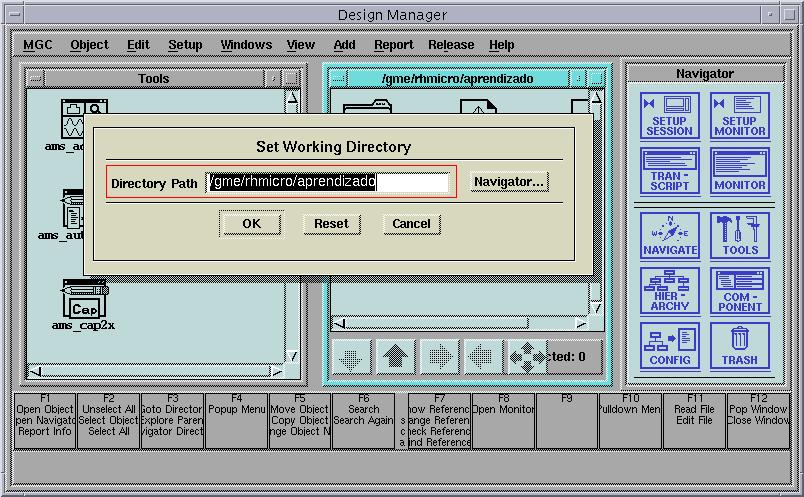

Nesta ferramenta podemos configurar o diretório de trabalho onde

estão os arquivos que descrevem o circuito ou sistema que irá

ser sintetizado pelo sistema Mentor. A figura 3.2 ilustra a configuração

do diretório (MGC > Set Working Directory)

4 Ferramenta: Design Architecture (da)

A ferramenta Design Architecture é responsável pelas entradas de descrição do circuito ou sistema e sua respectiva edição e compilação lógica. As entradas podem ser descritas em VHDL, ou utilizando outras linguagens de auto nível, ou através de esquemáticos.

4.1 Chamada da ferramenta

A ferramenta Design Architecture deve ser chamadas de dentro

do Design Manager. Entretanto, se for necessário chamar a

ferramenta isoladamente, digite o comando:

> da &

Para o ambiente AMS, digitar:

> ams_da &

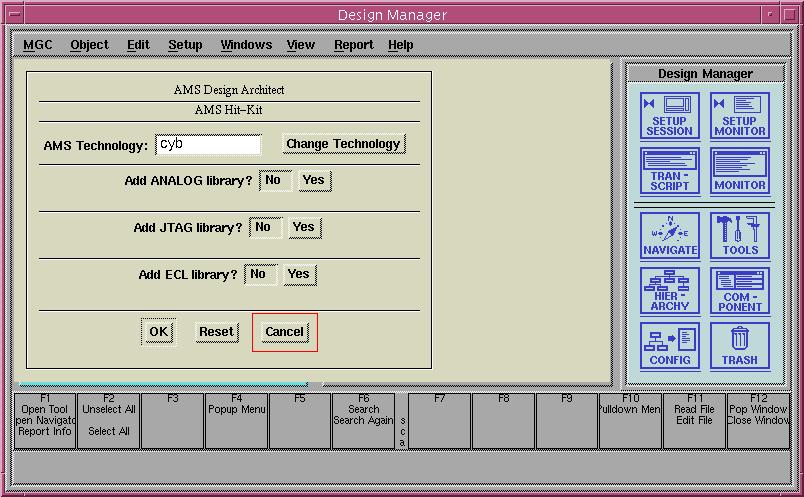

A figura 4.1 ilustra a chamada do Design Architecture de dentro do ams_dmgr. A tecnologia a ser escolhida para a síntese de layout deverá ser a tecnologia CMOS cyb.

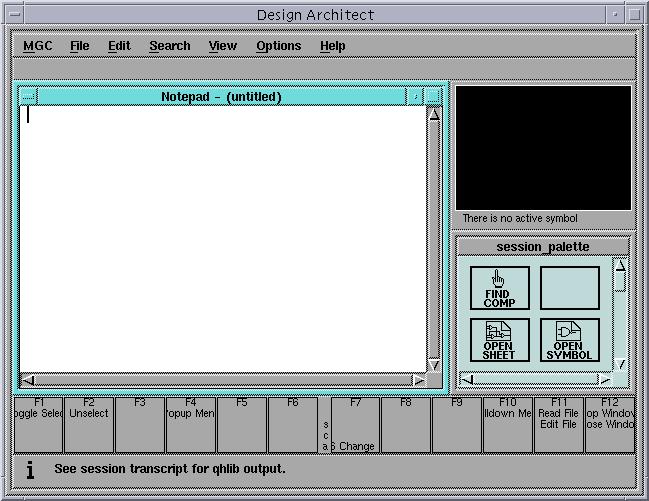

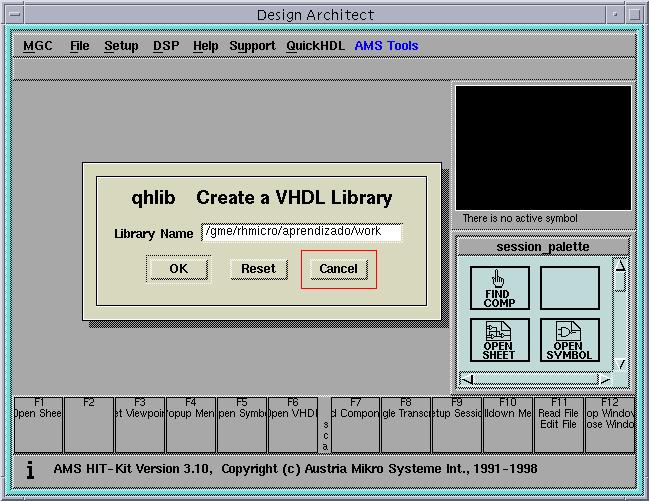

O circuito que iremos descrever em VHDL é um somador de 8 bits com carry de entrada e carry de saída. Para descrever um circuito em VHDL na ferramenta Design Architecture é necessário chamar um bloco de notas de dentro da ferramenta, como mostra a figura 4.2. Após, devemos escolher o diretório da biblioteca VHDL de utilização com o comando qlib, figura 4.3.

Arquivo VHDL do somador de 8 bits:

LIBRARY

ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

entity

somador8 is

PORT (

a : IN

bit_vector (7 downto 0);

b : IN

bit_vector (7 downto 0);

cin :

IN bit;

s : OUT

bit_vector (7 downto 0);

cout :

OUT bit

);

end somador8;

ARCHITECTURE

part OF somador8 IS

signal

cy : bit_vector (7 downto 0);

BEGIN

s(0) <=

a(0) xor b(0) xor cin;

s(1) <=

a(1) xor b(1) xor cy(0);

s(2) <=

a(2) xor b(2) xor cy(1);

s(3) <=

a(3) xor b(3) xor cy(2);

s(4) <=

a(4) xor b(4) xor cy(3);

s(5) <=

a(5) xor b(5) xor cy(4);

s(6) <=

a(6) xor b(6) xor cy(5);

s(7) <=

a(7) xor b(7) xor cy(6);

cy(0)

<= (a(0) and b(0)) or (a(0) and cin) or (b(0) and cin);

cy(1)

<= (a(1) and b(1)) or (a(1) and cy(0)) or (b(1) and cy(0));

cy(2)

<= (a(2) and b(2)) or (a(2) and cy(1)) or (b(2) and cy(1));

cy(3)

<= (a(3) and b(3)) or (a(3) and cy(2)) or (b(3) and cy(2));

cy(4)

<= (a(4) and b(4)) or (a(4) and cy(3)) or (b(4) and cy(3));

cy(5)

<= (a(5) and b(5)) or (a(5) and cy(4)) or (b(5) and cy(4));

cy(6)

<= (a(6) and b(6)) or (a(6) and cy(5)) or (b(6) and cy(5));

cy(7)

<= (a(7) and b(7)) or (a(7) and cy(6)) or (b(7) and cy(6));

cout <=

cy(7);

END;

Para compilar o circuito escolha no Menu superior o comando Compile.

Observação importante: Se o sistema esta descrito

em diversas entidades, o nome da arquitetura deve ser sempre explicitamente

especificada na entidade. Isso é devido ao Mentor possibilitar múltiplas

arquiteturas para uma mesma entidade.

Se as entidades estão descritas em arquivos fisicamente separados

(.vhd) deve-se definir o diretório onde estes arquivos se encontram

no Setup do Design Architecture.

5 Ferramenta: Simulador QuickSim

5.1 Chamada da ferramenta

As ferramentas devem ser chamadas de dentro do Design Manager. Entretanto, se for necessário chamar a ferramenta isoladamente, digite o comando:

> quicksim &

Informações a serem inseridas no Tutorial.

6 Ferramenta: Autologic II (alui)

6.1 Chamada da ferramenta

As ferramentas devem ser chamadas de dentro do Design Manager.

Entretanto, se for necessário chamar a ferramenta isoladamente,

digite o comando:

> alui &

Para o ambiente AMS, digitar:

> ams_alui &

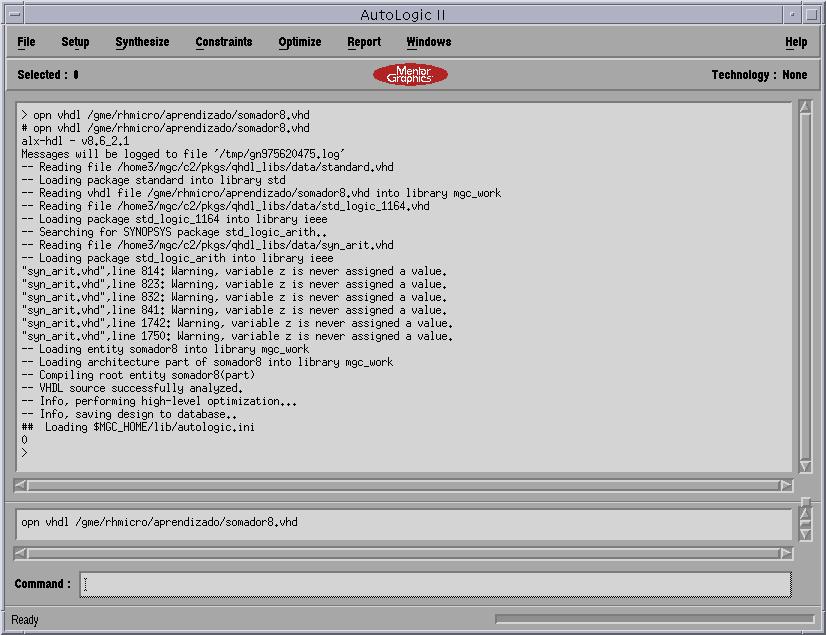

A descrição VHDL deve ser chamada pelo Menu File > Open > VHDL.

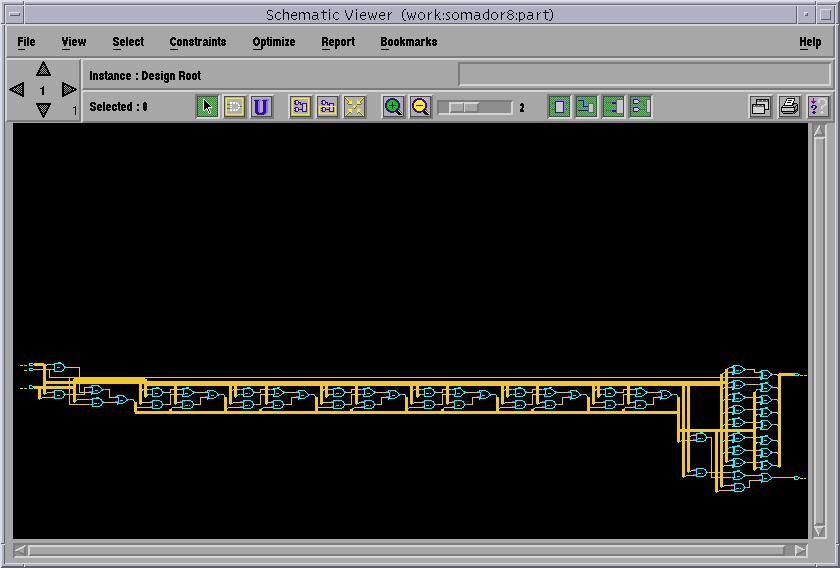

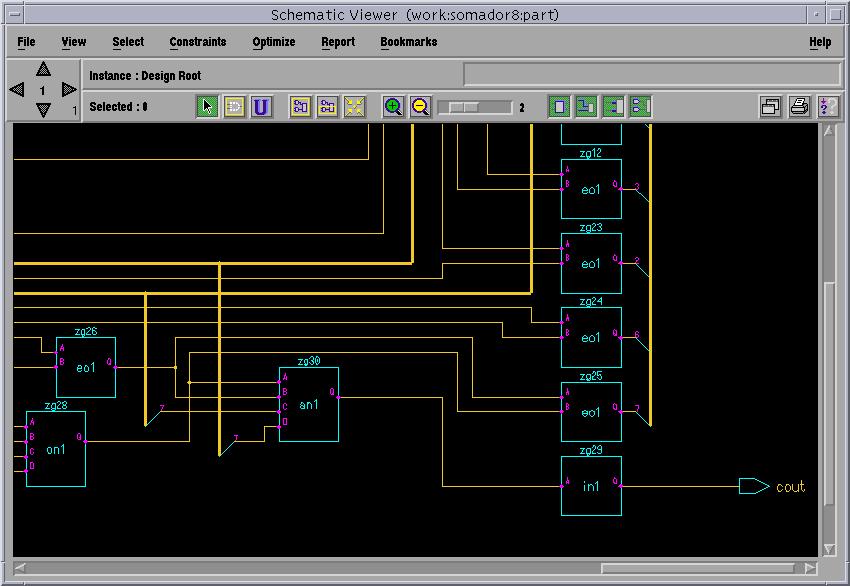

Nesta etapa serão criadas duas janelas, uma que mostrará a hierarquia do projeto, figura 6.2. E outra que mostrará o esquemático do projeto mapeado para uma biblioteca standard do Mentor, figura 6.3.

Para visualizar a janela do esquemático selecione Menu > Report > Schematic. Após a visualização da primeira versão do esquemático, feche a janela. Se quiser salvar o esquemático File > SAVE > *.sch.

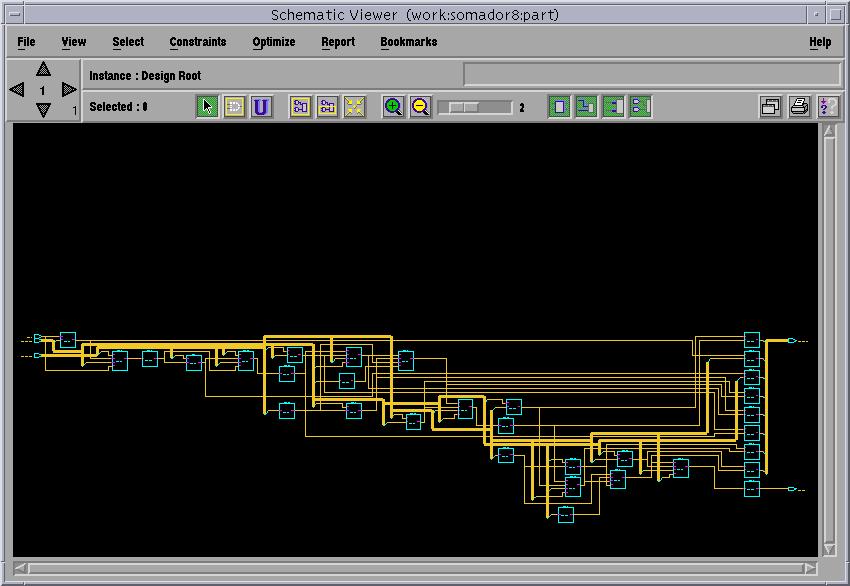

O segundo passo é escolher a biblioteca da AMS pelo Menu > Setup > Destination technology > AMS_CYB. E após escolhida a biblioteca destino da AMS, executamos o comando de Optimize > Optimize > Area. A sintese e otimização é realizada nessa etapa.

Para visualizar o novo esquemático contendo as células da AMS, execute o mesmo comando feito anteriormente, no Menu > Report > Schematic. Note que agora o esquemático está otimizado e utilizando as células descritas na biblioteca da AMS.

A figura 6.5 mostra um detalhe do esquemático final.

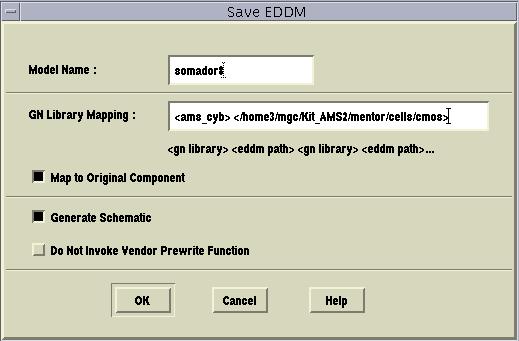

Para criar o layout deve-se salvar o projeto com a extensão EDDM

como mostrado na janela a baixo.

Execute o comando FILE > Save as > EDDM.

O GN library mapping é o mesmo para todos os projetos (diretório

de instalação do Mentor no grupo GME).

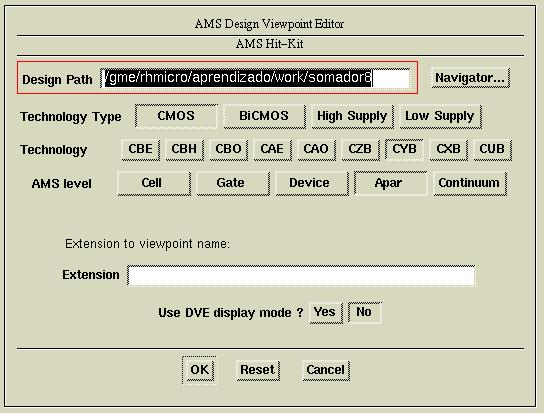

7 Ferramenta: Design View Point (DVE)

O Design View Point é um arquivo (.dve) que aponta para o circuito que estamos utilizando para simular ou para gerar o layout.

7.1 Chamada da ferramenta

As ferramentas devem ser chamadas de dentro do Design Manager.

Entretanto, se for necessário chamar a ferramenta isoladamente,

digite o comando:

> dve&

Para o ambiente AMS, digitar:

> ams_dve &

Neste caso, será necessário digitar outros comandos de configuração que virão escritos na tela, como tecnologia, nível de descrição, Se a ferramenta for chamada de dentro do ams_dmgr, veremos:

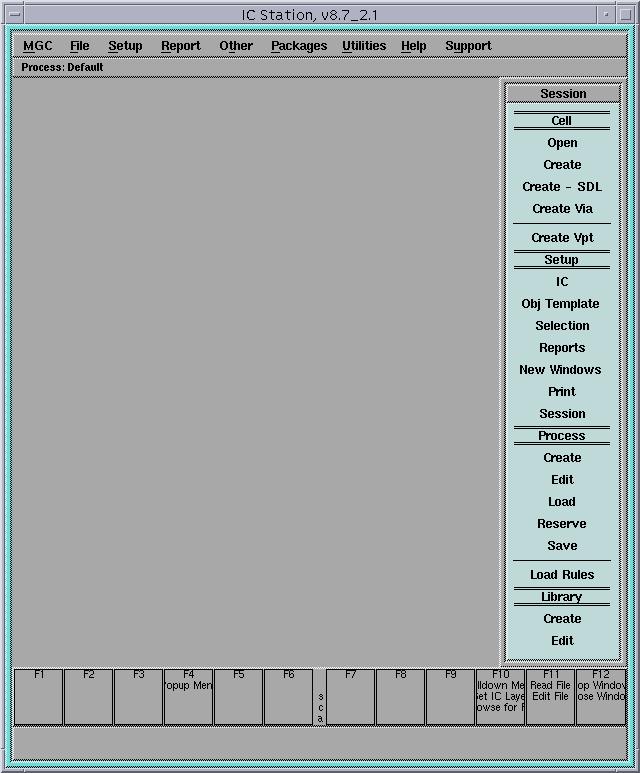

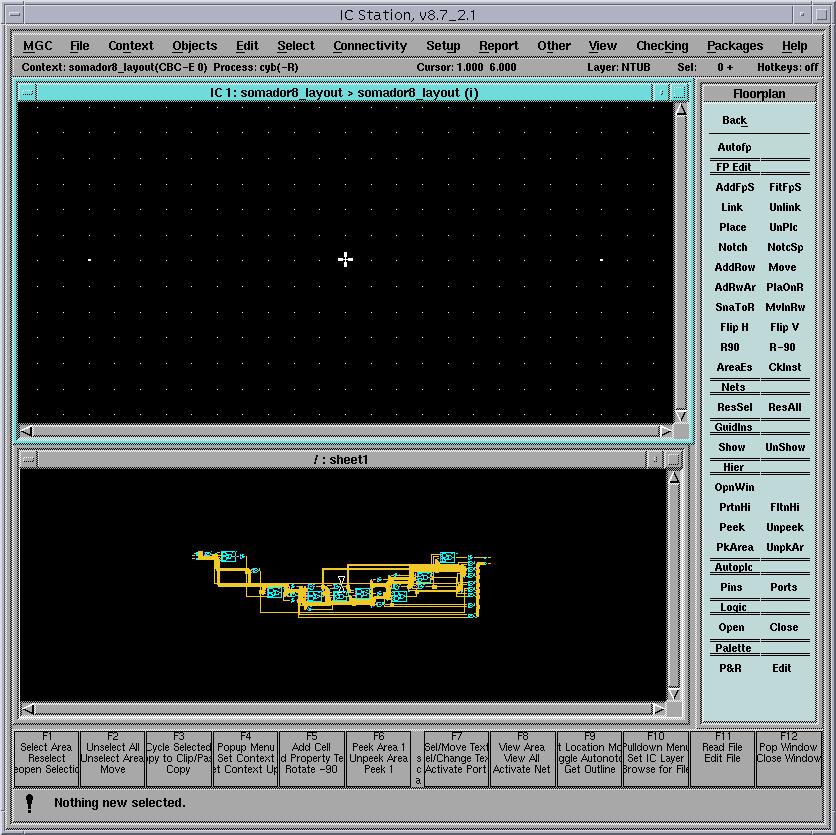

A ferramenta IC station é responsável pelo geração do layout. Podemos usar essa ferramenta para desenhar layout retângulo por retângulo (células ou circuitos menos complexos), editar layout, inserir novas tecnologias, ou para gerar automaticamente layout do tipo Standard Cell.

8.1 Chamada da ferramenta

Atenção: O IC station é a única ferramenta que deverá ser chamada obrigatoriamente fora do ambiente AMS para a geração automática de layout.

> ic &

A configuraração da biblioteca AMS é feita quando um novo layout é criado.

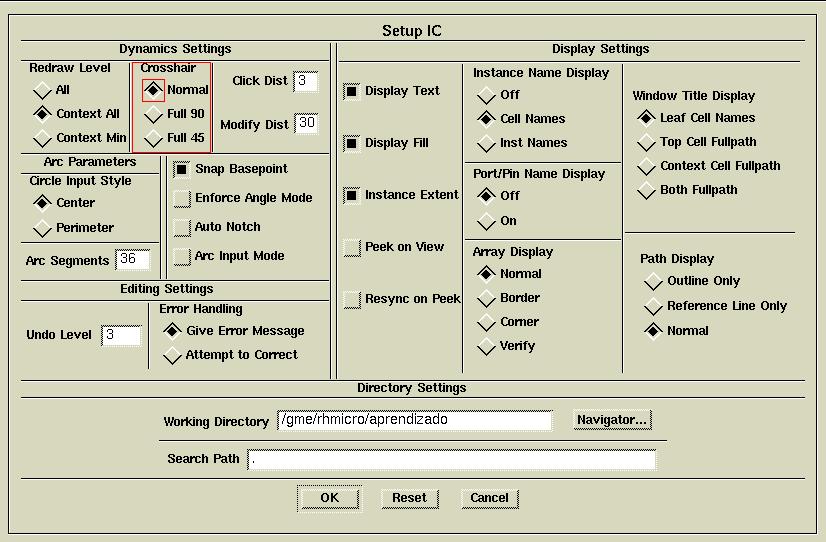

Primeiro devemos configurar o ambiente com o comando no menu lateral Setup > IC. Configuramos o Working Directory e o Search path (se necessário).

Observação importante sobre o Search Path: Se o layout a ser gerado contiver apenas células básicas da AMS (ou seja, a descrição não contem blocos hierarquicos), o search path não precisa ser definido. Porem, se o layout contiver blocos hierarquicos internos, o diretório que contem esses blocos de layout gerados previamente deve ser definido no search path.

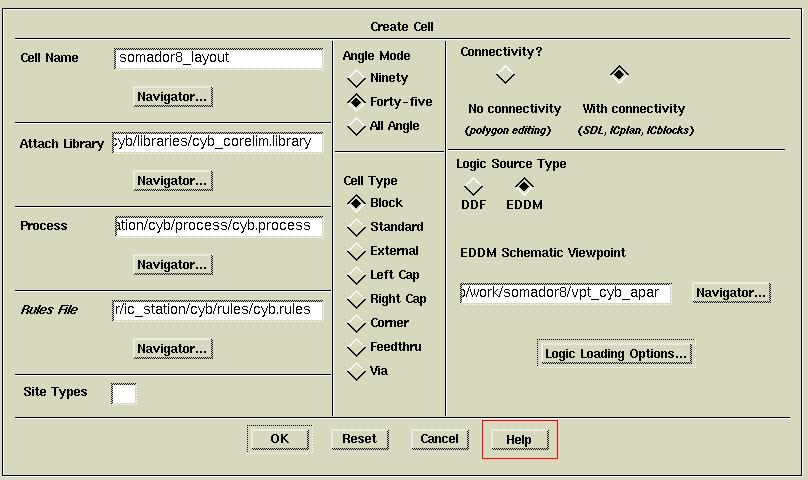

Figura 8.2 Criando uma nova célula de layout no IC Station

A criação do layout deve ser feita com o comando no menu

lateral Create > Cell.

Os diretórios da biblioteca AMS são os seguintes (execute

o browse):

Attach Library:

/home3/mgc/AMS_KIT2/mentor/ic_station/cyb/libraries/cyb_core

Process:

/home3/mgc/AMS_KIT2/mentor/ic_station/cyb/process/cyb

Rules Files:

/home3/mgc/AMS_KIT2/mentor/ic_station/cyb/rules/cyb

Cell Type: Escolha Block

se o layout contiver blocos hierarquicos ou Standard

se o layout contiver apenas células básicas da AMS (neste

caso escolha um Site Types diferente de zero). Se optar em usar sempre

Block, funciona para ambos os casos.

EDDM Schematic Viewpoint: escolha o diretório

onde foi criado o View Point (tem um formado diferenciado).

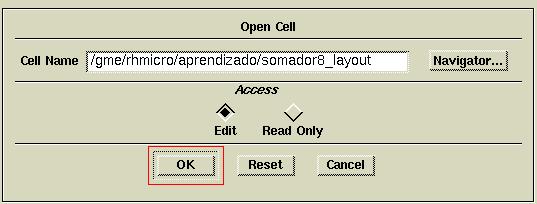

Após a criação da nova célula (create cell),

deve-se fecha-la e abri-la novamente no modo de edição como

mostrado na figura a seguir.

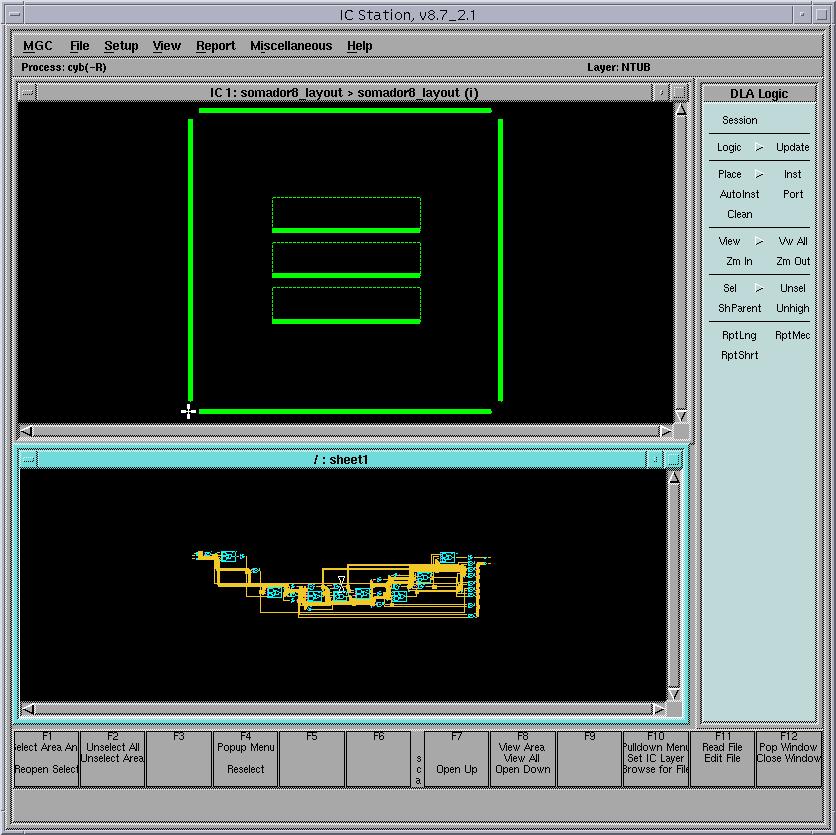

Para ver o esquemático correspondente ao layout que vai ser gerado (esquemático relacionado ao viewpoint), escolha a barra de menu a direita Floorplan e a opção Logic > open.

Após escolha a opção de Autofloorplan (Autofp) no menu da direita. Desta forma será gerada automaticamente uma estrutura de matriz com bandas e a borda dos pads na periferia como mostra a figura 8.6.

Figura 8.6 Planejamento das células de layout no IC Station

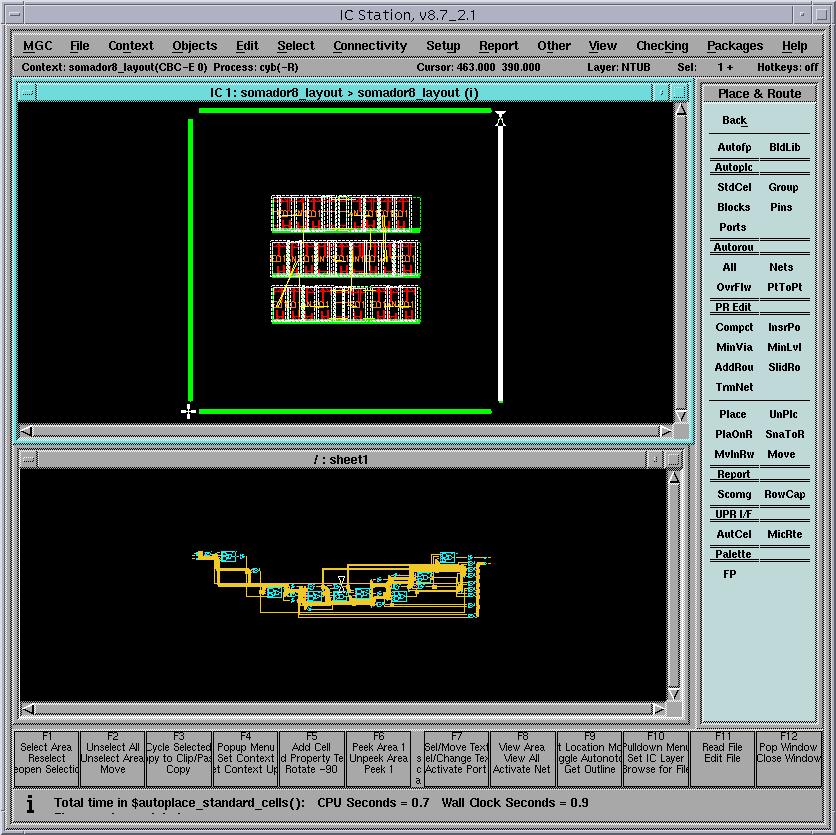

O placement é realizado na opção Autoplc. Como estamos posicionando células básicas (standard cell), então optamos pelo comando Autoplc > Stdcel. Se o projeto fosse hierarquico e tivesse diversos blocos internos, deveríamos primeiro fazer o layout de cada bloco (com standard cells) e após criar um novo layout que irá chamar os blocos já projetados (comando Autoplc > blocks).

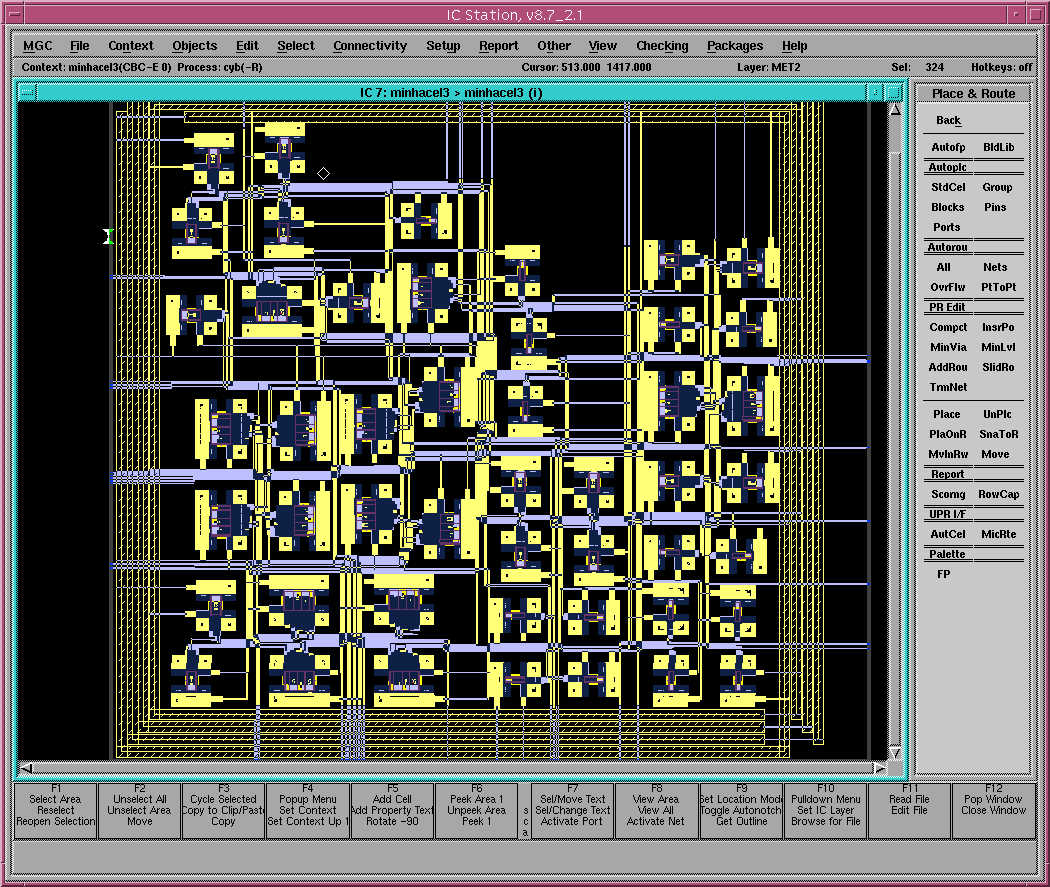

A figura 8.7 mostra as células do somador posicionadas nas bandas

da matriz standard cell.

Para ver o layout interno detalhado de cada célula da AMS, basta

seleciona-la, ir no Menu superior em Context > Hierarchy

> Peek. Escolha o nível (1).

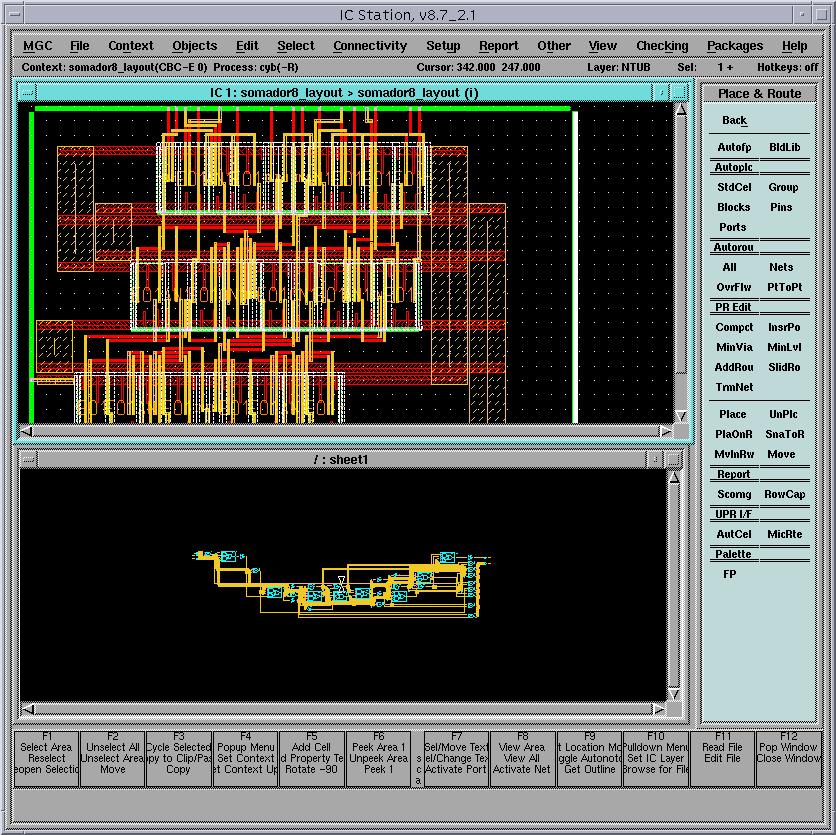

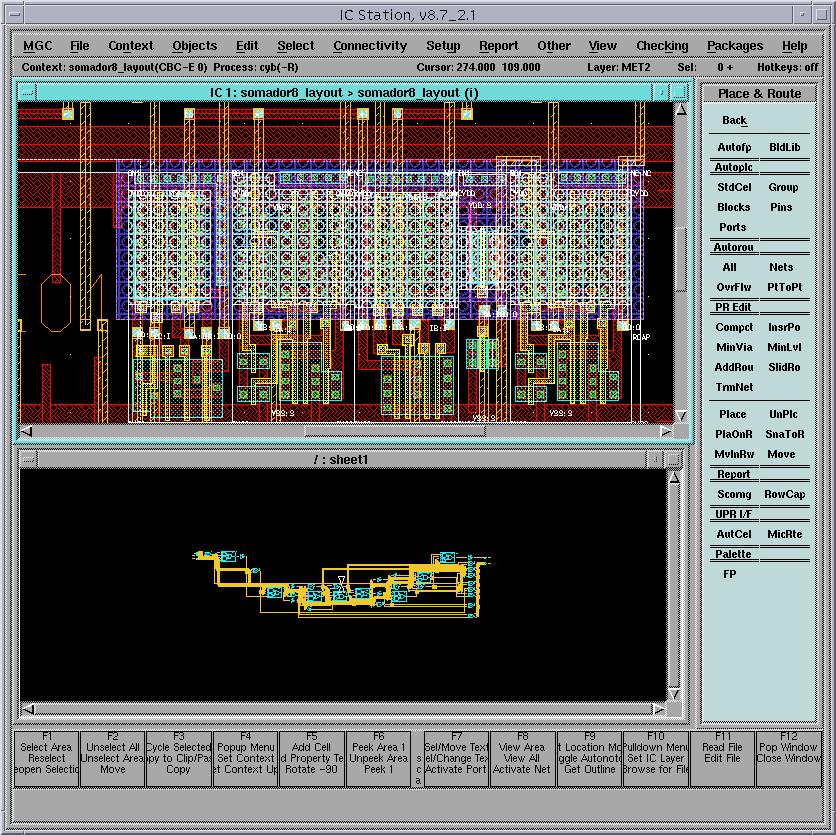

Para o roteamento automático escolha no menu lateral Autorou > all. O roteamento geral e detalhado é feito nesta etapa. Se houver overflow, ou seja, se algumas conexões não forem transformadas em roteamento, selecione cada conexão não roteada e execute o comando Autorou > OverFlw.

A figura 8.9 mostra o layout final detalhado.

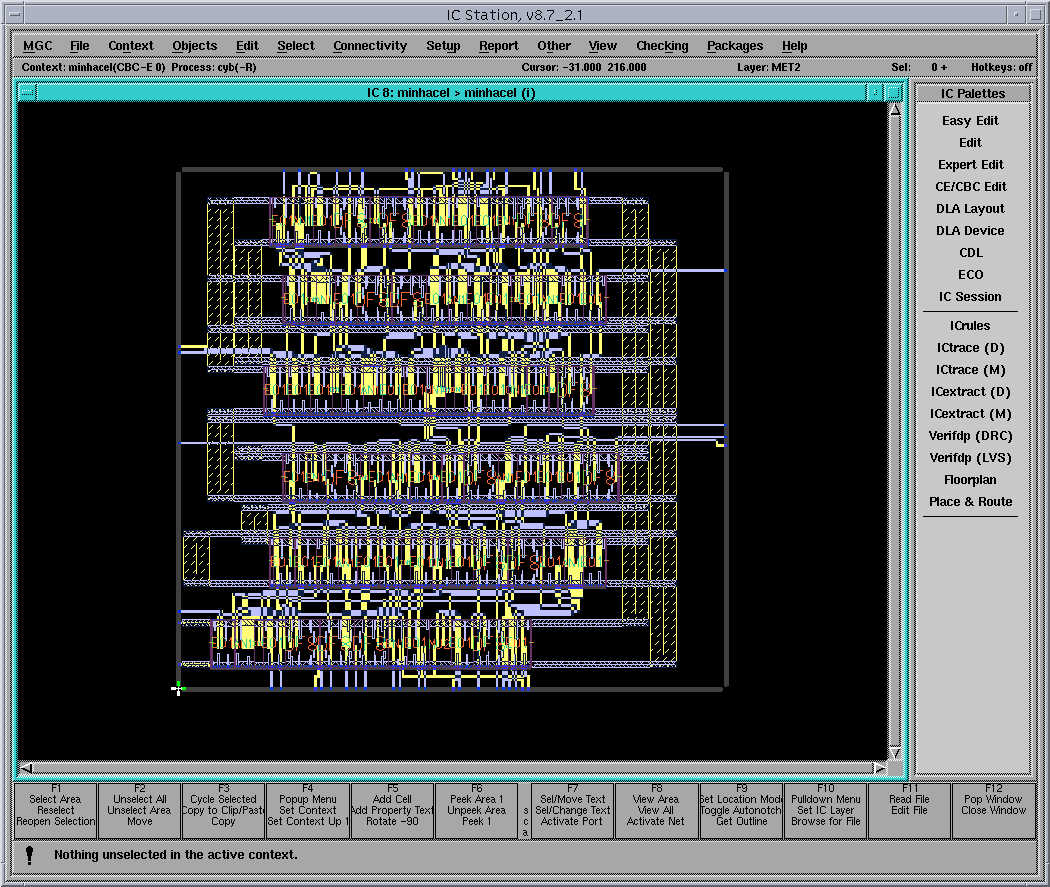

A figura 8.10 mostra um exemplo de layout composto por blocos hierarquicos que foram instanciados no layout. E a figura 8.11 mostra o mesmo circuito com um layout feito totalmente em Standard Cell. Note que o layout composto por blocos não ficou muito compactado, na verdade está 4 vezes maior que o segundo.

Figure 8.10 - Layout de um somador composto por blocos hierarquicos.

Figure 8.11 - Layout de um somador composto por apenas portas lógicas

básicas.

A inserção dos pads deve ser feita hierarquicamente no Design Arquitecture (da). Os pads são células da biblioteca AMS. Desta forma quando o layout for gerado, haverá um bloco central que comtém todo o layout do circuito já roteado e os pads ao redor. Nesta etapa deve ser realizado apenas o roteamento dos pinos do CORE (bloco central) aos pads.

Algumas questões em aberto:

1) Colocar passo a passo a inserção

dos pads e depois a geração do layout final com os pads.

2) Como gerar um layout composto apenas por células

básicas quando o circuito esta descrito hierarquicamente (diversas

entidades)?

Possível resposta, durante a síntese

no Alui pode haver uma opção em realizar a síntese

hierarquica ou não. Vantagem em descrever um circuito em diversas

entidades: circuito mudular, fácil compreensão. Vantagem

do layout sem hierarquia: compactação. As opções

dependem do circuito e da aplicação.

3) Passos para realizar a extração

elétrica e simulação.

Este tutorial apresentou apenas os passos básicos para geração de um layout a partir de uma descrição VHDL no sistema Mentor. A sua contribuição é muito importante para completar este Tutorial. Mande um e-mail para mim fglima@inf.ufrgs.br para inserir itens e dados neste tutorial.

Muito Obrigada!

Fernanda