INF01058

# Circuitos Digitais

Resumo Parasitas RC em Portas CMOS Alta Impedância

Aula 4a

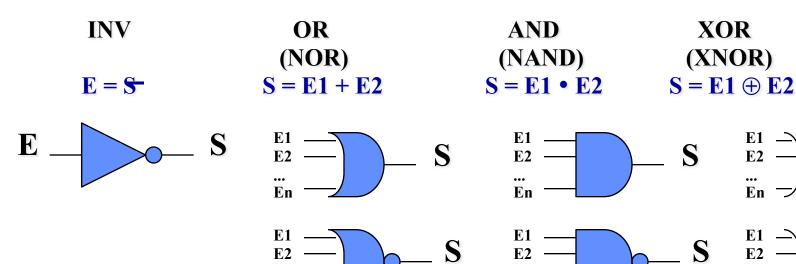

### Portas Lógicas (revisão ...)

| $\mathbf{E}$ | INV |

|--------------|-----|

| 0            | 1   |

| 1            | 0   |

| '            |     |

... En

| <b>E</b> 1 | <b>E2</b> | AND | NAND | OR | NOR | XOR | XNOR |

|------------|-----------|-----|------|----|-----|-----|------|

| 0          | 0         | 0   | 1    | 0  | 1   | 0   | 1    |

| 0          | 1         | 0   | 1    | 1  | 0   | 1   | 0    |

| 1          | 0         | 0   | 1    | 1  | 0   | 1   | 0    |

| 1          | 1         | 1   | 0    | 1  | 0   | 0   | 1    |

|            |           |     |      | l  |     |     |      |

... En

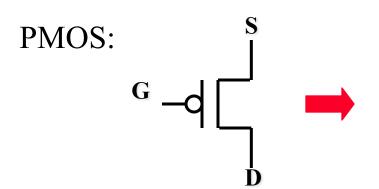

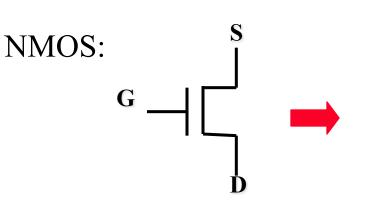

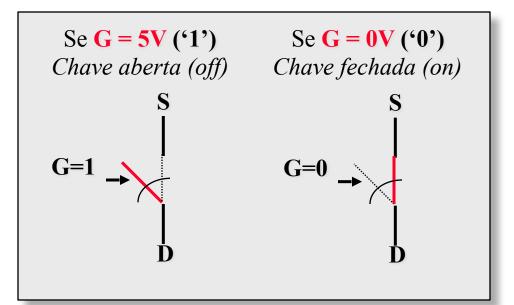

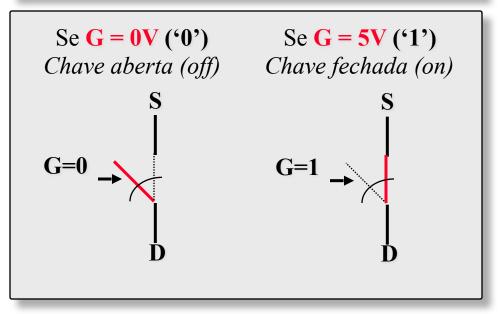

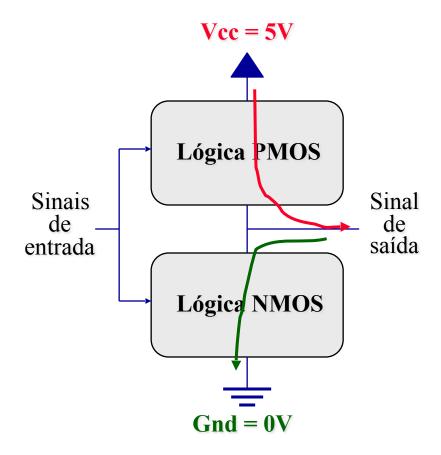

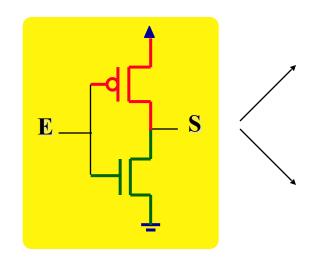

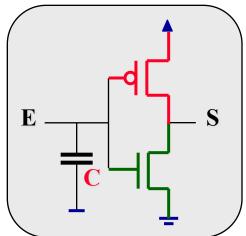

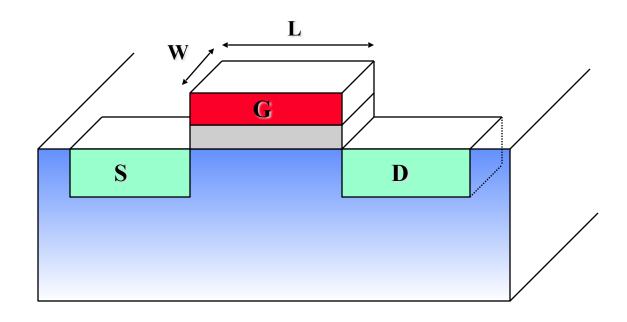

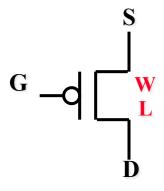

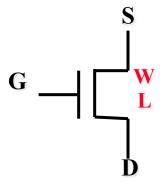

## Transistores PMOS e NMOS (revisão ...)

#### Porta Lógica CMOS (revisão)

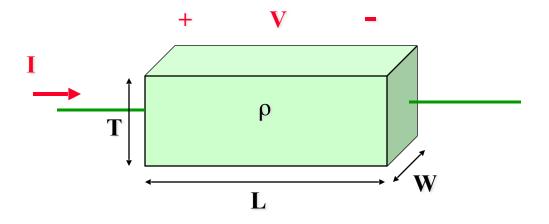

#### Resistência (R)

$$\mathbf{R} = \rho \cdot \frac{L}{W \cdot T}$$

Lei de Ohm:

$$R = V / I$$

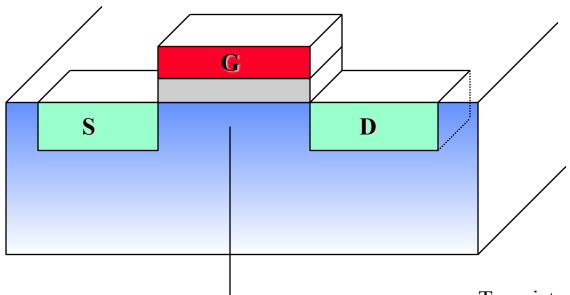

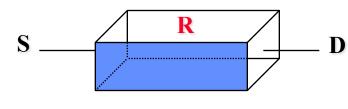

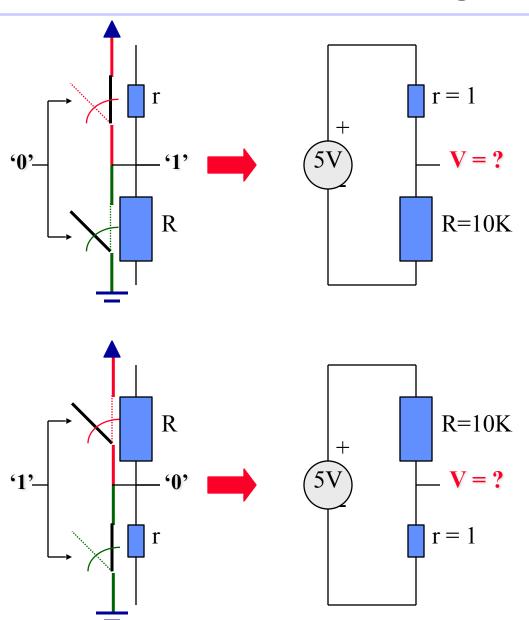

#### Resistência de Canal do Transistor

canal do transistor

- Transistor não é 'chave ideal'.

- Canal do transistor ⇒ resistência

- Transistor conduzindo: resistência pequena ( $R \Rightarrow 0$ )

- Transistor 'cortado': resistência muito alta  $(R \Rightarrow \infty)$

# Inversor CMOS: (resistência parasita)

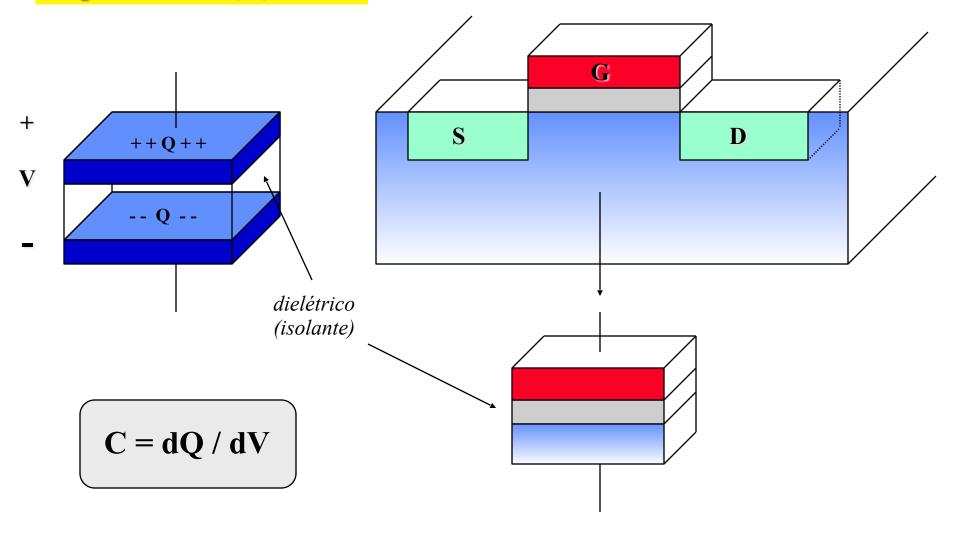

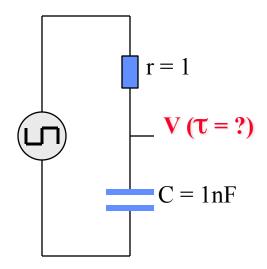

### Capacitância (C)

# Inversor CMOS: (capacitância parasita)

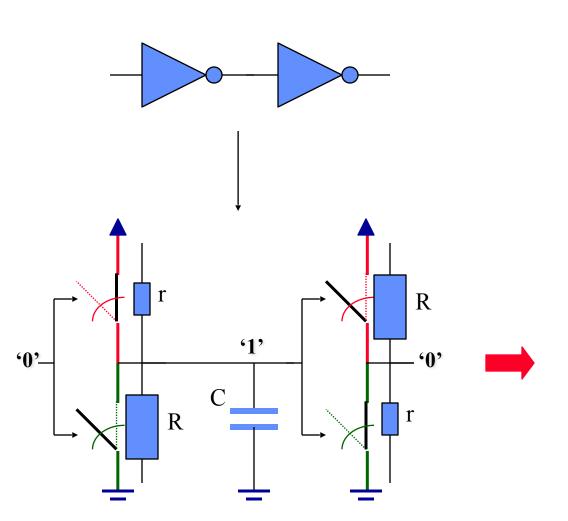

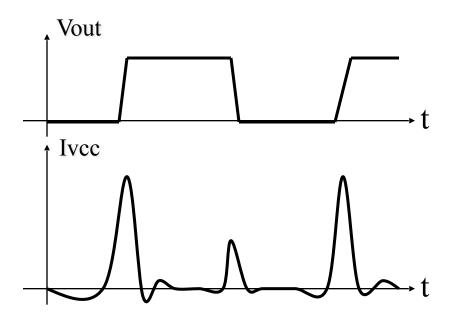

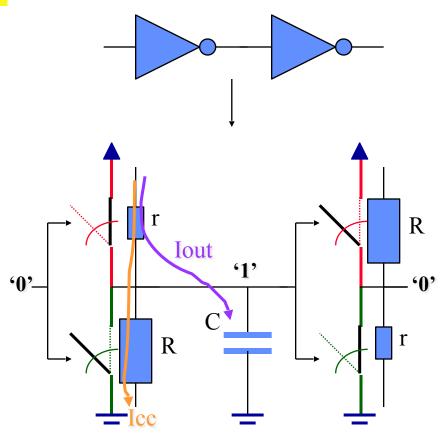

#### Consumo (Dissipação de Potência)

- Corrente de Carga: Iout

- Corrente de Curto-Circuito: Icc

- consumo estático : antigamente  $\approx 0$

- consumo dinâmico (transição) = Iout + Icc

- consumo total = estático + dinâmico

\* A variação de W e L afeta o tempo de transição dos sinais e o consumo da porta lógica.

#### **Dimensionamento do Transistor MOS**

Análise de 'r' ('on') e C:

- W  $\uparrow$  :  $r \downarrow e C \uparrow$

- L  $\uparrow$  : r  $\uparrow$  e C  $\uparrow$

### Alta Impedância (Z)

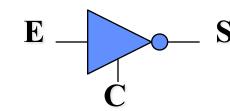

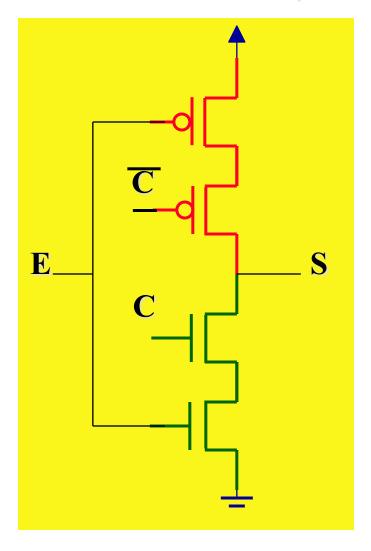

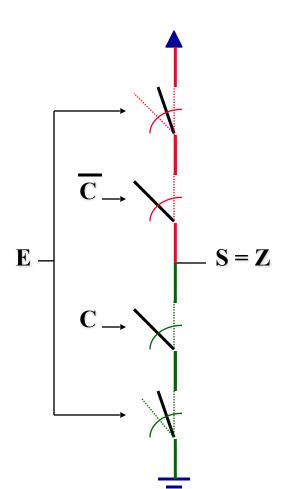

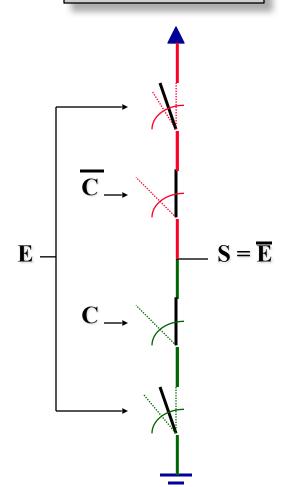

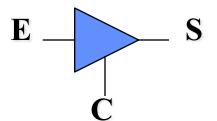

#### **Inversor Tri-State (INVTR)**

| E | C | C | S |

|---|---|---|---|

| 0 | 0 | 1 | Z |

| 1 | 0 | 1 | Z |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 |

ou

ou

Outra opção... (controle negado)

| E | C | S |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 1 | Z |

| 1 | 1 | Z |

|   |   |   |

$\begin{array}{c|c}

C & S \\

\hline

0 & E \\

1 & Z

\end{array}$

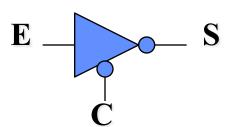

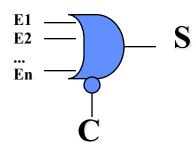

**Buffer Tri-State** (**BUFTR**)

| <u> </u> |

|----------|

| 0        |

| 1        |

| Z        |

| Z        |

|          |

$\begin{array}{c|c} C & S \\ \hline 0 & Z \\ 1 & E \end{array}$

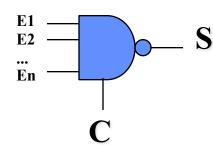

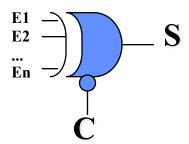

\* PODE-SE PENSAR EM QUALQUER PORTA LÓGICA COM SAÍDA TRI-STATE OU ALTA-IMPEDÂNCIA (Z) !!!

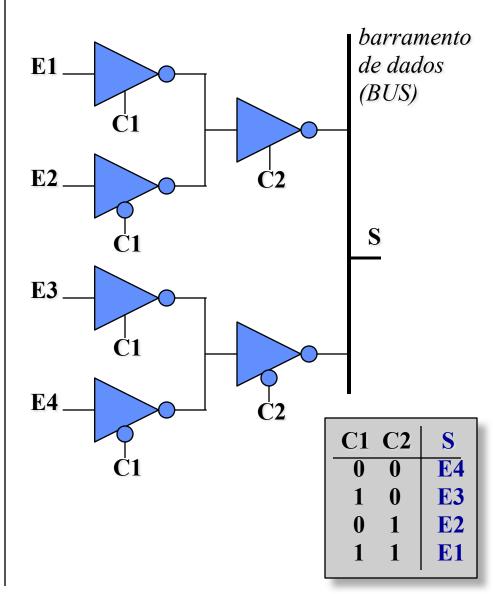

#### **Uso de Porta Tri-State...**

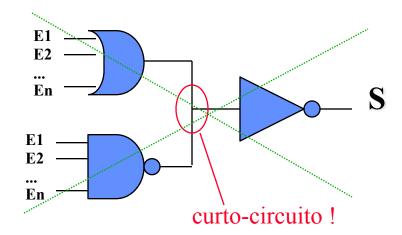

#### \* NÃO É PERMITIDO EM CMOS:

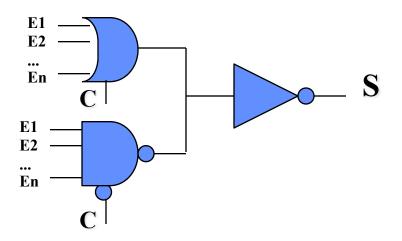

#### \* CORRETO:

#### \* BARRAMENTO DE SINAIS :