INF01058

# Circuitos Digitais

Portas Lógicas CMOS: Aspectos Temporais e Elétricos

Aula 4b

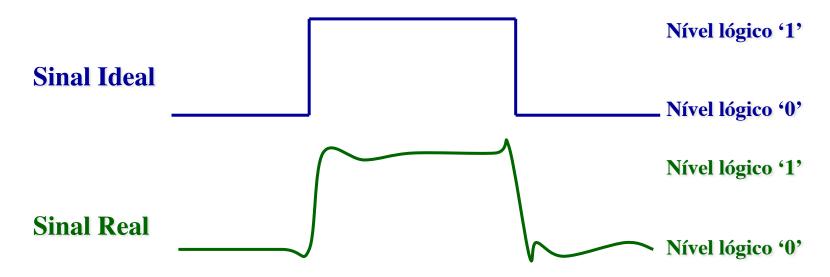

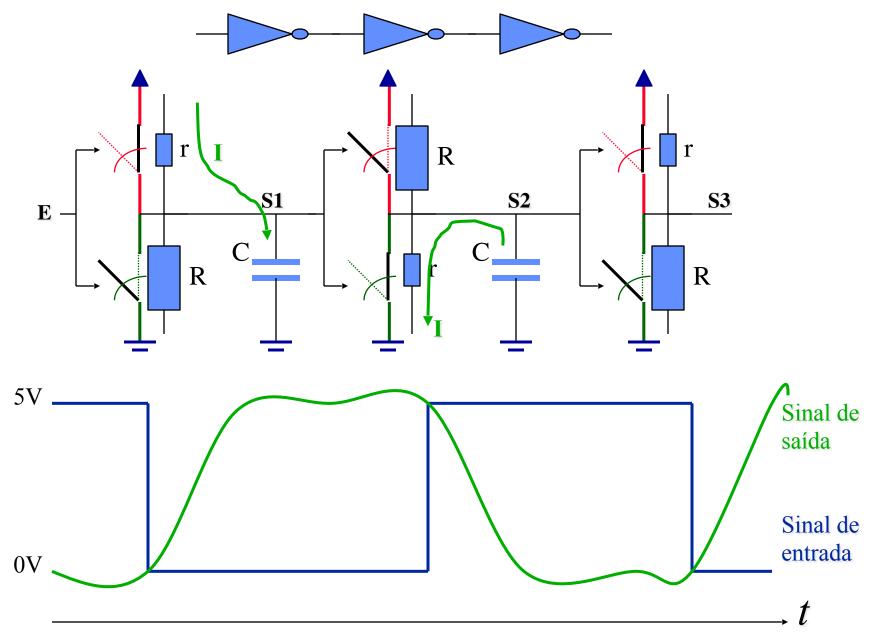

#### Chaveamento

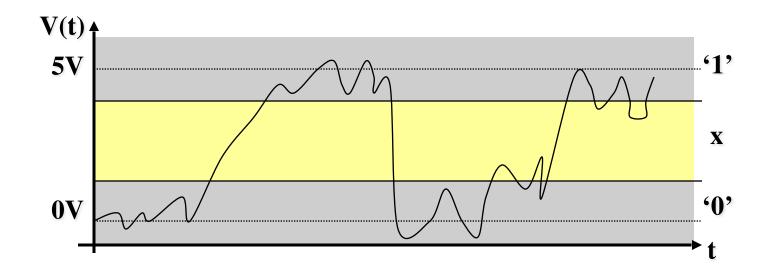

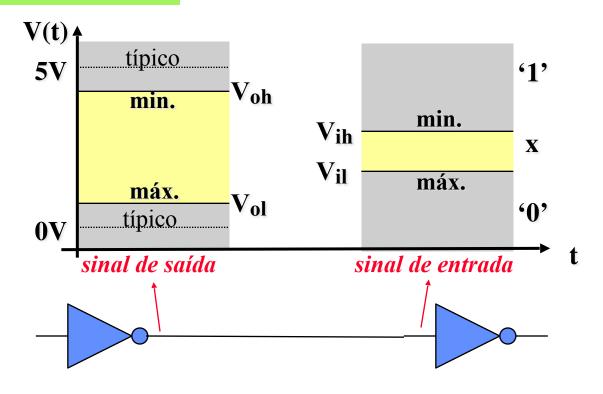

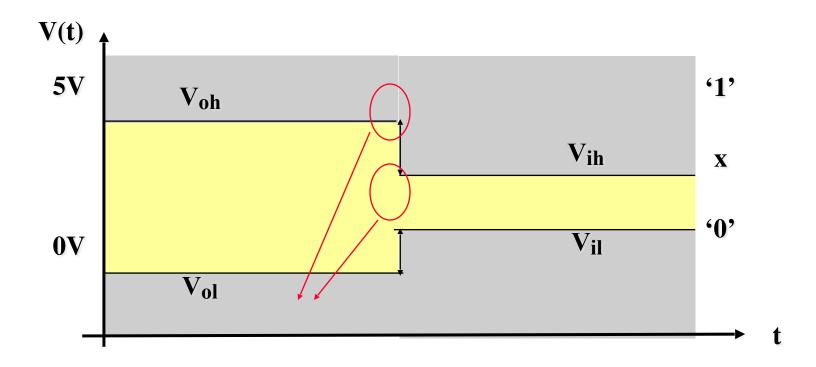

#### Níveis de Tensão

- V<sub>il</sub> máx. maior tensão de entrada aceitável como sendo nível lógico '0'

- Vih min. menor tensão de entrada aceitável para nível lógico '1'

- Vol típico tensão normalmente gerada na saída da porta lógica para nível lógico '0'

- V<sub>oh</sub> típico tensão normalmente gerada na saída da porta lógica para nível lógico '1'

- Vol máx. maior tensão encontrada na saída da porta lógica para nível lógico '0'

- V<sub>oh</sub> min. menor tensão encontrada na saída da porta lógica para nível lógico '1'

### Margem de Ruído

<sup>\*</sup> O menor valor dessas diferenças é que define a Margem de Ruído!!!

# Características Temporais (timing)

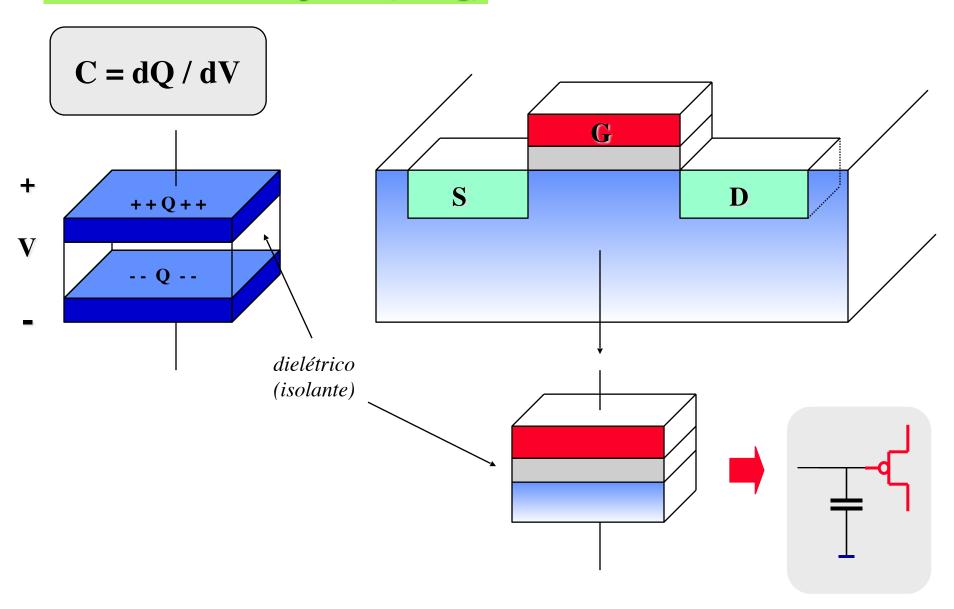

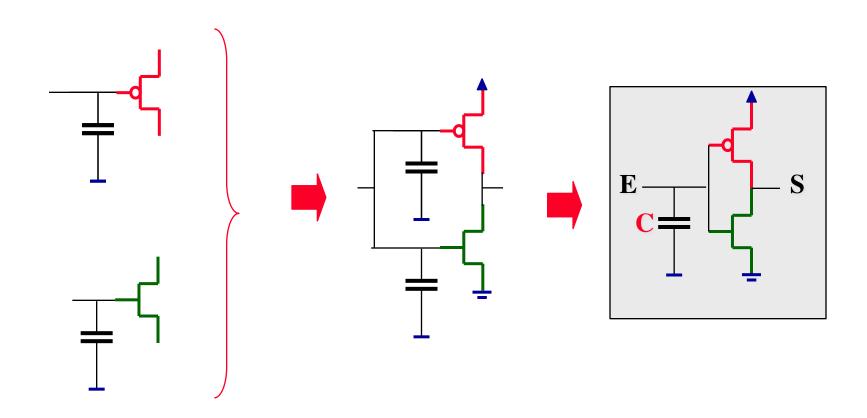

# Capacitância de 'Gate'

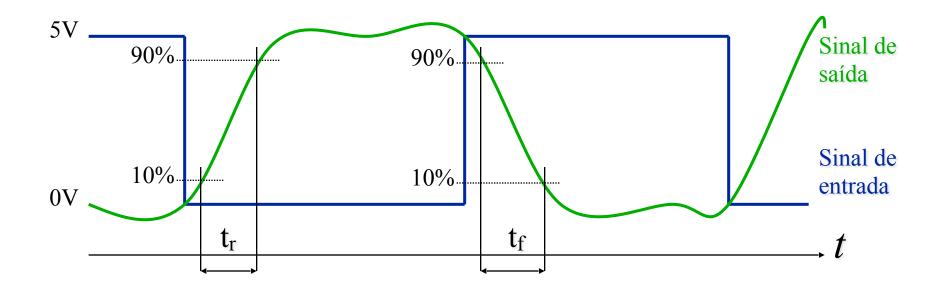

#### Tempos de subida e descida

- t<sub>r</sub> Tempo de subida (*rise time*)

- t<sub>f</sub> Tempo de descida (fall time)

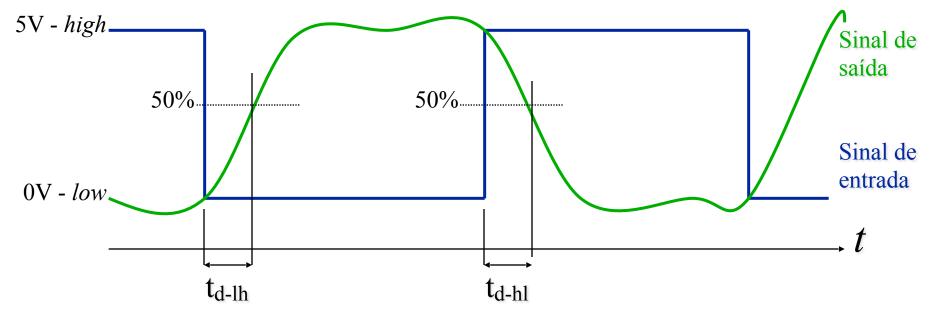

#### Tempo de Propagação de um Sinal

- t<sub>d-lh</sub> Tempo de atraso de propagação do sinal de saída quando este passa do nível lógico '0' para o nível lógico '1' (*delay time \_ low-high*)

- t<sub>d-hl</sub> Tempo de atraso de propagação do sinal de saída quando este passa do nível lógico '1' para o nível lógico '0' (*delay time \_ high-low*)

- t<sub>d</sub> Tempo de atraso de propagação MÉDIO do sinal de saída (*delay time*)

$$\mathbf{t_d} = (\mathbf{t_{d-lh}} + \mathbf{t_{d-hl}}) / 2$$

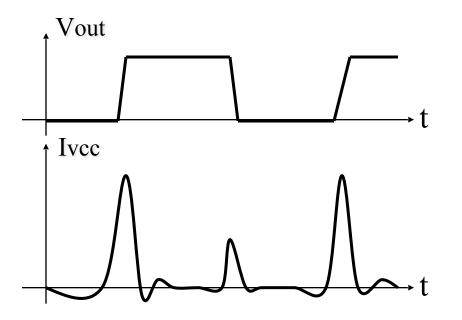

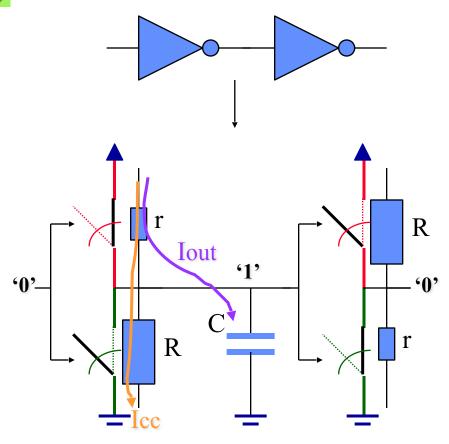

## Consumo (Dissipação de Potência)

- Corrente de Carga: Iout

- Corrente de Curto-Circuito: Icc

- consumo estático ≈ 0

- consumo dinâmico (transição) = Iout + Icc

- consumo total = estático + dinâmico

\* A variação de W e L afeta no tempo de transição dos sinais e no consumo da porta lógica.

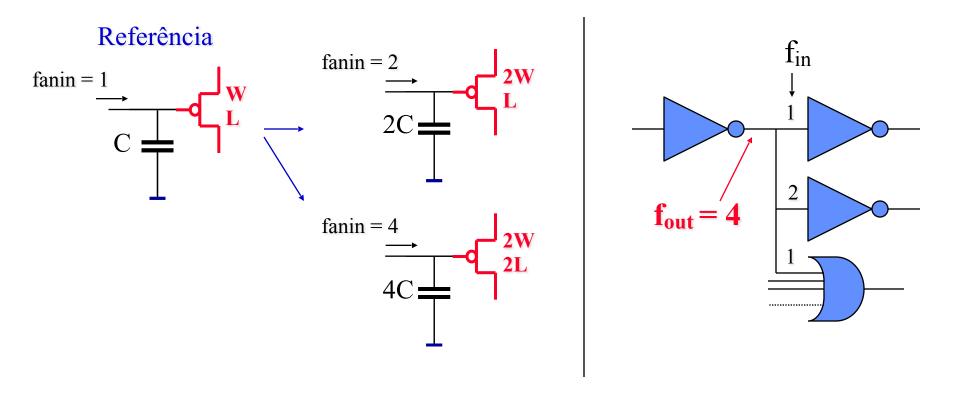

## **Fanin e Fanout**

- Fanin (f<sub>in</sub>) é o valor da capacitância de entrada normalizada em função de uma capacitância de referência.

- Fanout (f<sub>out</sub>) é a soma das capacitâncias de entrada normalizadas que uma porta lógica tem conectada a sua saída.

O fanout de uma porta lógica afeta diretamente as características de tempo de propagação do sinal de saída (atraso) e consumo de corrente (potência) fornecida pela Fonte de Tensão.

#### Exemplo:

| td   | $f_{out} = 1$ | $f_{out} = 2$ | $f_{out} = 3$ | ••• |

|------|---------------|---------------|---------------|-----|

| INV  | 1ns           | 1.2ns         | 1.4ns         |     |

| AND2 | 2ns           | 2.5ns         | 3ns           |     |

| XOR3 | 1.5ns         | 1.7ns         | 1.9ns         |     |

|      |               |               |               |     |

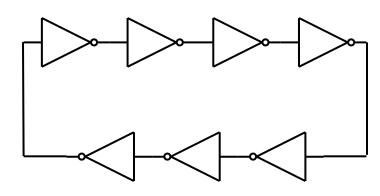

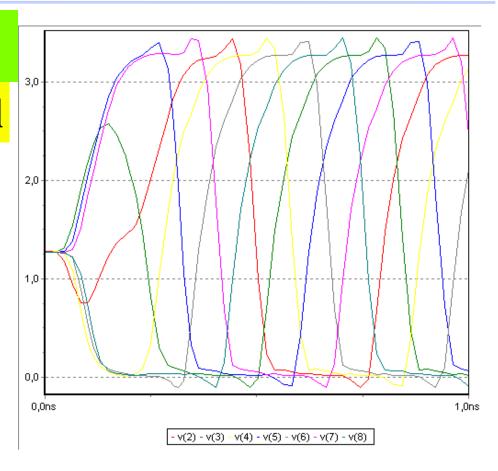

# Estudo de caso INVERSORES em Anel

O que é?

N inversores em anel.

- Variação contínua 0--> 1 --> 0--> em cada nó se N é ímpar.

- Conhecido como " oscilação" ou "corrida" se N é ímpar

- Latch bi-estável de N é par.

Resultado de Simulação Elétrica com Simulador SPICE para N=7.

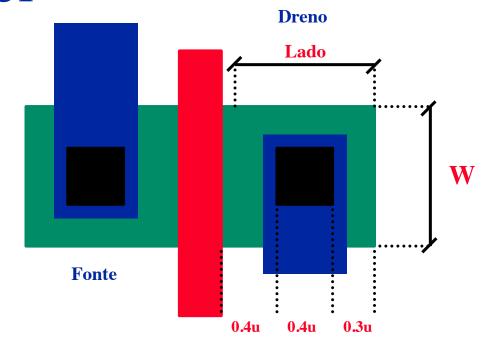

# Capacitâncias/Resistências em um Transistor

W (largura) do transistor (Exemplo 1 um)

L (comprimento) do transistor (Exemplo 0,3um)

AD=1.1P PD=3.2U AS=1.1P PS=3.2U AD=1.1P PD=3.2U AS=1.1P PS=3.2U

Para AMS 0,35u

Área = W \* Lado Perímetro = 1\*W + 2\*Lado