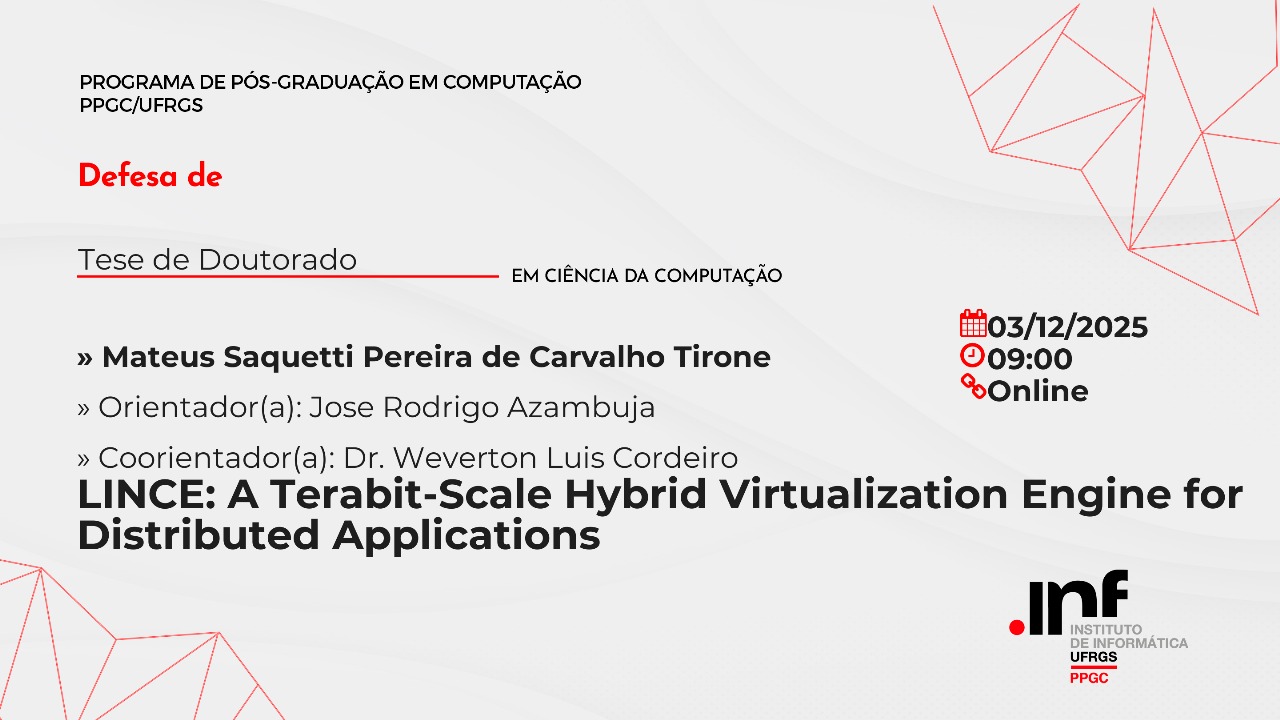

Defesa – Tese de Mateus Tirone

Aluno(a): Mateus Saquetti Pereira de Carvalho Tirone

Orientador(a): Jose Rodrigo Furlanetto de Azambuja

Coorientador(a): Dr. Weverton Luis da Costa Cordeiro

Título: LINCE: A Terabit-Scale Hybrid Virtualization Engine for Distributed Applications

Linha de Pesquisa: Sistemas Embarcados

Data: 03/12/2025

Hora: 09:00

Local: Esta banca ocorrerá de forma híbrida (virtual e presencial), na sala 43412/215 do Instituto de Informática/UFRGS e pelo link https://meet.google.com/ppt-wazf-mve.

Banca Examinadora:

-Gabriel Luca Nazar (UFRGS)

-Fernanda Gusmão de Lima Kastensmidt (UFRGS)

-Monica Magalhães Pereira (UFRN)

Presidente da Banca: Jose Rodrigo Furlanetto de Azambuja

Resumo: The rise of data-intensive, latency-sensitive applications necessitates a shift towards In- Network Computing (INC). However, a significant gap persists: existing academic FPGA- based platforms lack terabit-scale performance, while commercial ASICs lack the flexibility and virtualization required for multi-tenant, programmable data planes. This thesis introduces LINCE (Line-rate In-Network Compute Engine), a novel hybrid FPGA-ASIC platform designed as a System-on-Chip that bridges this gap. LINCE synergizes the high-speed performance of an ASIC for static I/O and queuing functions with the dynamic reconfigurability of an FPGA for hosting parallel, isolated In-Network Computing units. The platform offers a versatile development ecosystem, supporting both the standard P4 language for network functions and a highly efficient C++/HLS workflow for complex, Turing-complete applications. The architecture is characterized to achieve an aggre gate virtualized throughput of 3.2 Tbps, an order of magnitude beyond prior academic solutions. Our C++/HLS flow is demonstrated to reduce resource utilization by up to 99.5% compared to traditional P4 toolchains while improving latency and throughput. The platform’s efficacy is validated through the successful deployment of sophisticated distributed applications, including line-rate Artificial Neural Network inference (achieving latencies under 1.5 ?s) and real-time, content-aware video stream processing (reducing critical packet loss by 82.5%). By reconciling terabit-scale performance with deep programmability and dynamic virtualization, LINCE establishes a new benchmark and provides a robust, open-source foundation for the next generation of intelligent networks.

Palavras-Chave: Programmable Data Planes, In-network Computing, FPGA, P4