Publicado em: 27/02/2024

IEEE CASS RS Talks 2024

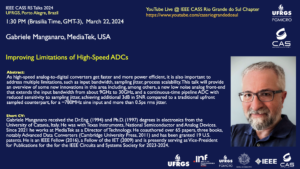

CASS Talk: Improving Limitations of High-Speed ADCs

No dia 22 de março às 13:30h (Horário de Brasília) ocorrerá a palestra “Improving Limitations of High-Speed ADCs” com Gabriele Manganaro – Diretor de Tecnologia da MediaTek (USA).

Para acessar a palestra, clique aqui.

YouTube Live @ IEEE CASS Rio Grande do Sul Chapter

Abstract:

As high-speed analog-to-digital converters get faster and more power efficient, it is also important to address multiple limitations, such as input bandwidth, sampling jitter, process scalability. This talk will provide an overview of some new innovations in this area including, among others, a new low noise analog front-end that extends the input bandwidth from about 9GHz to 30GHz, and a continuous-time pipeline ADC with reduced sensitivity to sampling jitter, achieving additional 3dB in SNR compared to a traditional upfront sampled counterpart, for a ~780MHz sine input and more than 0.5ps rms jitter.

Short CV:

Gabriele Manganaro received the Dr.Eng. (1994) and Ph.D. (1997) degrees in electronics from the University of Catania, Italy. He was with Texas Instruments, National Semiconductor and Analog Devices. Since 2021 he works at MediaTek as a Director of Technology. He coauthored over 65 papers, three books, notably Advanced Data Converters (Cambridge University Press, 2011) and has been granted 19 U.S. patents. He is an IEEE Fellow (2016), a Fellow of the IET (2009) and is presently serving as Vice-President for Publications for the for the IEEE Circuits and Systems Society for 2023-2024.