Publicado em: 20/03/2025

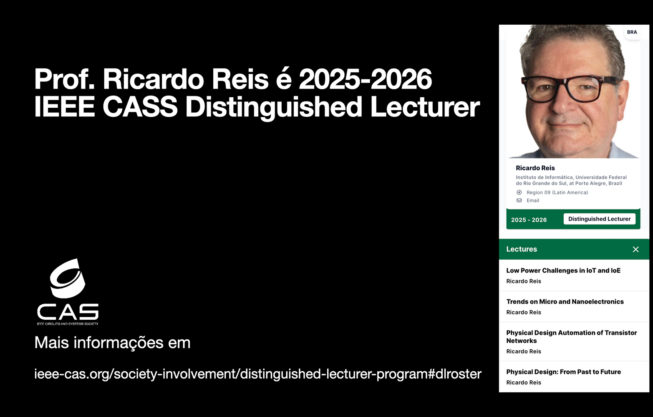

Prof. Reis é DL IEEE CASS 2025-2026

O prof. Ricardo Reis é Distinguished Lecturer da IEEE Circuits and Systems Society pela segunda vez, no periodo de 2025-2026.

O prof. Ricardo Reis é Distinguished Lecturer da IEEE Circuits and Systems Society pela segunda vez, no periodo de 2025-2026. Na primeira vez, foi entre 2014-2015. Qualquer CASS Chapter no mundo pode convidar um DL Speaker e a IEEE CASS cobre os gastos de viagem. O Prof. Reis é também DL da IEEE Council on EDA (2024-2025).

Mais informações aqui.

As 4 palestras oferecidas são:

1- Low Power Challenges in IoT and IoE

Abstract

The increasing number of devices connected to the internet is providing the concept of Internet of Things, that together with Internet of Health, Internet of People and Internet of Something is constructing the Internet of Everything (IoE). There is also an overlapping between IoT and CPS (Cyber Physical Systems) that have as components not only electronic ones, but also mechanical components, optical components, organic components, chemical components, etc. A keyword in IoT is optimization, mainly power optimization. Power optimization must be done in all levels of design abstraction, and at physical level is related to the number of transistors. Also, many systems are critical ones, like in Internet of Heath, where reliability is a major issue. Most of the circuits designed nowadays use much more transistors than it is needed. The increasing leakage power and routing issues are an important reason to optimize the number of transistors, as leakage power is related to the number of transistors. Also, the replacement of a set of basic gates by a complex gate reduces the number of connections to be implemented using metal layers as well the number of vias. The reduction of the number of connections to be implemented using metal layers helps to improve routing and also helps to improve reliability. To cope with this goal, it is needed to provide tools to automatically generate the layout of any transistor network.

2- Trends on Micro and Nanoelectronics

Abstract

The talk starts with a short presentation of Electronics and Microelectronics evolution. Then, it will be presented a set of several trends in the design of micro and nanoelectronics circuits, including architectural issues, variability and sources of variability, EDA tools, physical design issues, printability, design of transistor networks, Layout Strategies, Regularity, 3D circuits, flexible electronics, new devices, Stretchable Silicon, Fault Tolerance, Tolerance to Radiation Effects, Factory Integration, … The talk tries to motivate the audience to explore the upcoming challenges in the field.

3- Physical Design Automation of Transistor Networks

Abstract

A way to reduce power consumption is to reduce the number of transistors used to implement a circuit, as leakage power is proportional to the number of transistors. It is shown a physical design approach to reduce the number of transistors needed to perform a task. It is proposed an EDA tool set to automatically generate the physical design of any transistor network. It shows an important reduction on power, improving also reliability. A standard cell library has a limited number of logical functions, and a limited number of sizings. The talk is target in optimization methods to reduce the number of transistors of a circuit. The methods allow the realization of any possible logical function or transistor network. It is included comparisons with solutions using the traditional standard cell methodology.

4- Physical Design: From Past to Future

Abstract

By the end of years 70s, microprocessors were designed by hand showing excellent layout compaction. It will be shown some highlights of the reverse engineering of the Z8000, which control part was designed by hand, showing several layout optimization strategies. The observation of the Z8000 layout inspired the research of methods to do the automatic generation of the layout of any transistor network, allowing to reduce the number of transistors to implement a circuit, and by consequence, the leakage power. Some of the layout automation tools developed by our group are briefly presented.