Publicado em: 01/09/2020

Ciclo de Palestras

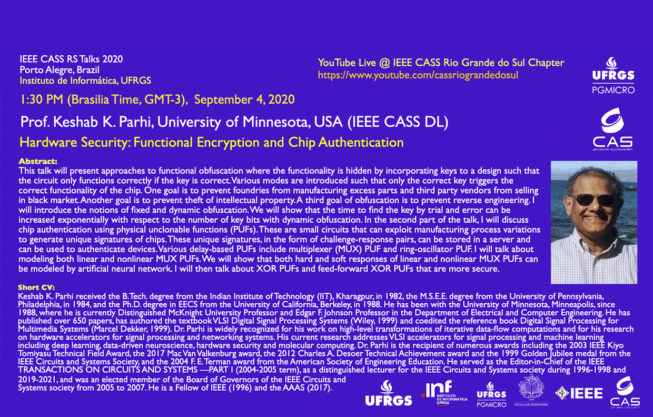

IEEE CASS RS Talks 2020

Nesta sexta-feira, dia 04/09 às 13h30min (Horário de Brasília) ocorrerá a palestra “Hardware Security: Functional Encryption and Chip Authentication” ministrada pelo Professor Keshab K. Parhi (University of Minnesota, USA). A transmissão será feita pelo canal do YouTube do IEEE CASS Rio Grande do Sul Chapter.

Esta palestra apresentará abordagens para “functional obfuscation” em que a funcionalidade é escondida pela incorporação de chaves a um projeto de forma que o circuito só funcione corretamente se a chave estiver correta. Vários modos são introduzidos de forma que apenas a tecla correta acione a funcionalidade correta do chip. Um dos objetivos é evitar que as fundições fabriquem peças excedentes e que fornecedores terceirizados vendam no mercado negro. Outro objetivo é evitar o roubo de propriedade intelectual. Um terceiro objetivo da ofuscação é evitar a engenharia reversa.

Será apresentada na palestra as noções de ofuscação fixa e dinâmica. Assim, será mostrado que o tempo para encontrar a chave por tentativa e erro pode ser aumentado exponencialmente em relação ao número de bits de chave com ofuscação dinâmica. Na segunda parte da palestra, será discutida a autenticação de chip usando funções físicas não clonáveis (PUFs). Esses são pequenos circuitos que podem explorar as variações do processo de fabricação para gerar assinaturas exclusivas de chips. Essas assinaturas exclusivas, na forma de pares de desafio-resposta, podem ser armazenadas em um servidor e podem ser usadas para autenticar dispositivos. Vários PUFs baseados em atraso incluem PUF multiplexador (MUX) e PUF de oscilador em anel.

O palestrante, Keshab K. Parhi, recebeu o B.Tech. grau do Instituto Indiano de Tecnologia (IIT), Kharagpur, em 1982, o M.S.E.E. diploma da University of Pennsylvania, Philadelphia, em 1984, e o Ph.D. graduado em EECS pela University of California, Berkeley, em 1988. Ele está na Universidade de Minnesota, Minneapolis, desde 1988, onde atualmente é Professor Distinto da Universidade McKnight e Professor Edgar F. Johnson no Departamento de Engenharia Elétrica e de Computação. Ele publicou mais de 650 artigos, foi autor do livro VLSI Digital Signal Processing Systems (Wiley, 1999) e co-editou o livro de referência Digital Signal Processing for Multimedia Systems (Marcel Dekker, 1999). O Dr. Parhi é amplamente reconhecido por seu trabalho em transformações de alto nível de cálculos de fluxo de dados iterativos e por sua pesquisa sobre aceleradores de hardware para processamento de sinais e sistemas de rede. Sua pesquisa atual aborda aceleradores VLSI para processamento de sinal e aprendizado de máquina, incluindo aprendizado profundo, neurociência baseada em dados, segurança de hardware e computação molecular.