Publicado em: 29/04/2021

Livro da Springer Nature em coautoria com Reis

A obra pretende ajudar os leitores a identificar o melhor projeto de circuito, considerando a aplicação alvo e os requisitos de projeto, como restrições de área ou limitações de potência/atraso

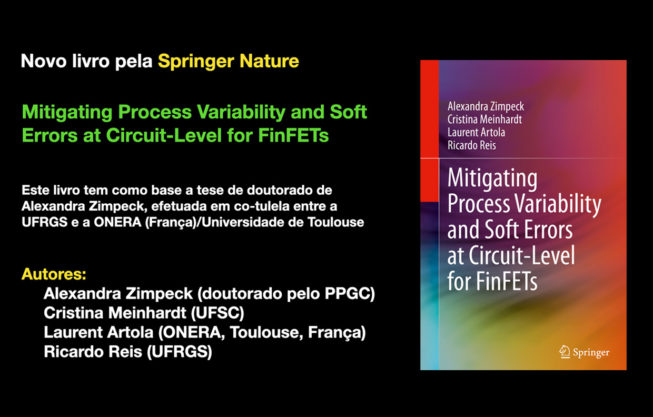

Este ano, o Professor Ricardo Reis foi convidado para contribuir em coautoria com Alexandra Zimpeck (doutorado pelo PPGC), Cristina Meinhardt (doutorado pelo PPGC e professora na UFSC) e Laurent Artola (ONERA, Toulouse, França), na produção do livro Mitigating Process Variability and Soft Errors at Circuit-Level for FinFETs, publicado recentemente pela Editora Springer Nature.

A obra avalia a influência das variações de processo (por exemplo, flutuações da função de trabalho) e soft-errors induzidos por radiação em um conjunto de células lógicas usando a tecnologia FinFET, considerando o nó tecnológico de 7 nm como um estudo de caso. Além disso, para uma estimativa precisa de soft-errors, os autores adotaram uma ferramenta geradora de eventos de radiação (MUSCA SEP3), que trata tanto dos recursos de leiaute quanto das propriedades elétricas dos dispositivos. Os autores também exploraram quatro técnicas em nível de circuito (por exemplo, reordenação de transistor, células de desacoplamento, Schmitt Trigger e sleep transistor) como alternativas para atenuar os efeitos indesejados em células lógicas FinFET.

Este livro também avalia a tendência de mitigação quando diferentes níveis de variação do processo, dimensionamento do transistor e características de partícula de radiação são aplicados no projeto. É efetuada uma comparação geral de todos os métodos abordados por este trabalho, permitindo traçar uma compensação entre os ganhos de confiabilidade e as penalidades de projeto de cada abordagem em relação à área, desempenho, consumo de energia, largura de pulso transiente de evento único (SET) e SET de corte transversal.

Explica como medir a influência da variabilidade do processo (por exemplo, flutuações de função de trabalho) e erros suaves induzidos por radiação em células lógicas FinFET e permite que os projetistas melhorem a robustez dos circuitos integrados FinFET sem se concentrar em ajustes de fabricação. Discute também os benefícios e desvantagens do uso de abordagens em nível de circuito, como reordenamento de transistor, células de desacoplamento, Schmitt Trigger e transistor de sono para mitigar o impacto da variabilidade do processo e erros suaves.

Assim, a obra avalia as técnicas descritas no contexto de diferentes cenários de teste: níveis distintos de variações de processo, dimensionamento do transistor e diferentes recursos de radiação, com isso, ajuda os leitores a identificar o melhor projeto de circuito, considerando a aplicação alvo e os requisitos de projeto, como restrições de área ou limitações de potência/atraso.

Para mais informações, acesse o site da Editora.